Q:基本RS锁存器存在不确定状态,本篇我们设计可以消除不确定状态的锁存器--逻辑门控D锁存器。

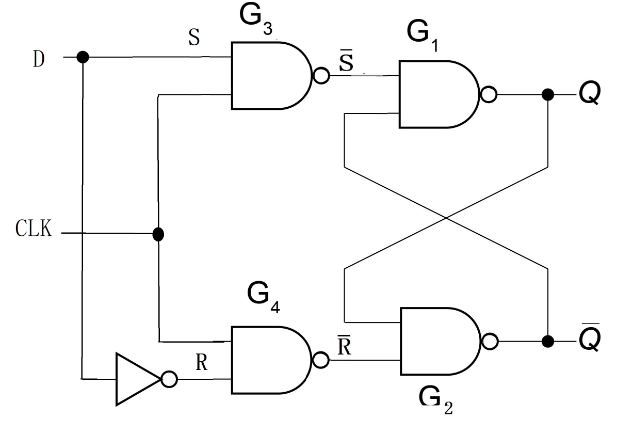

A:逻辑门控D锁存器逻辑图:

其工作原理:在CLK=1期间,数据输入端D的值被传输到输出端Q,而当CLK由1 跳变为0时,锁存器将保持跳变之前瞬间D的值。

(1)当CLK=0时,,无论D取何值,输出Q和

都保持不变。

(2)当CLK=1且D=1时, ,

,因此Q被置1;当CLK=1且D=0时,

,

,因此Q被置0。

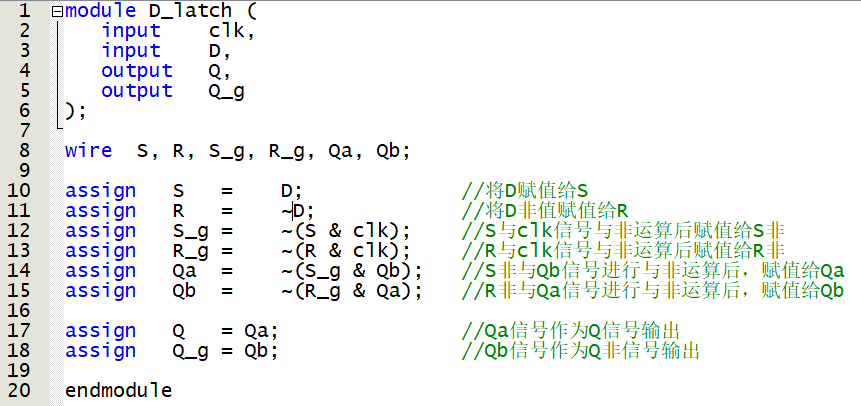

部分Verilog HDL代码:

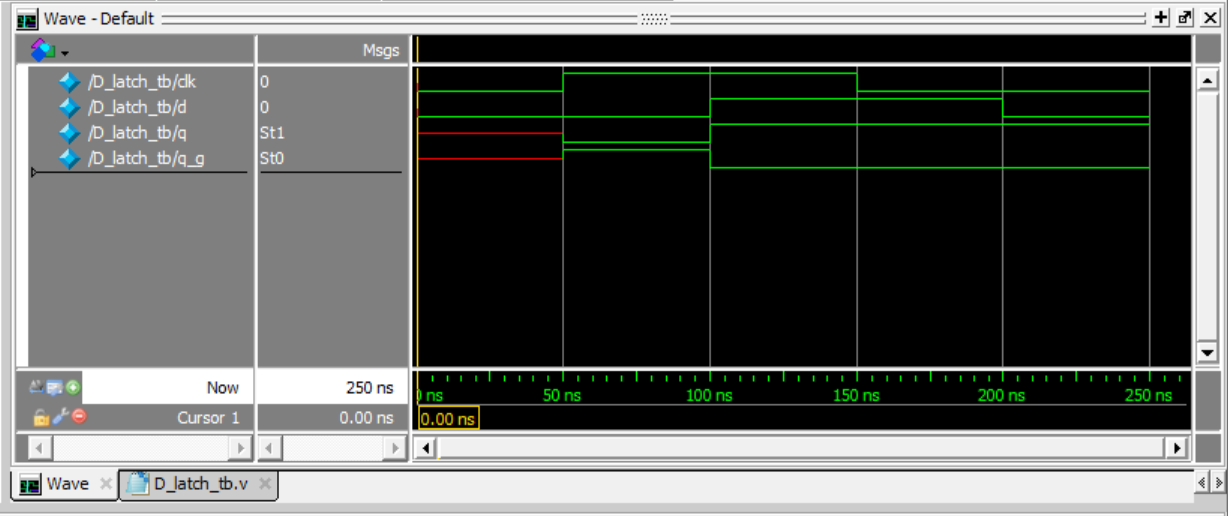

与基本RS触发器一样,使用DE2-115开发板的SW[1:0]做为2个输入端;LEDR[1:0]显示输出状态。ModelSim仿真结果:

本文介绍了如何设计逻辑门控D锁存器以解决基本RS锁存器的不确定状态问题,通过VerilogHDL编程并用DE2-115开发板进行模型仿真,验证了该锁存器在不同输入条件下的稳定工作特性。

本文介绍了如何设计逻辑门控D锁存器以解决基本RS锁存器的不确定状态问题,通过VerilogHDL编程并用DE2-115开发板进行模型仿真,验证了该锁存器在不同输入条件下的稳定工作特性。

5078

5078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?