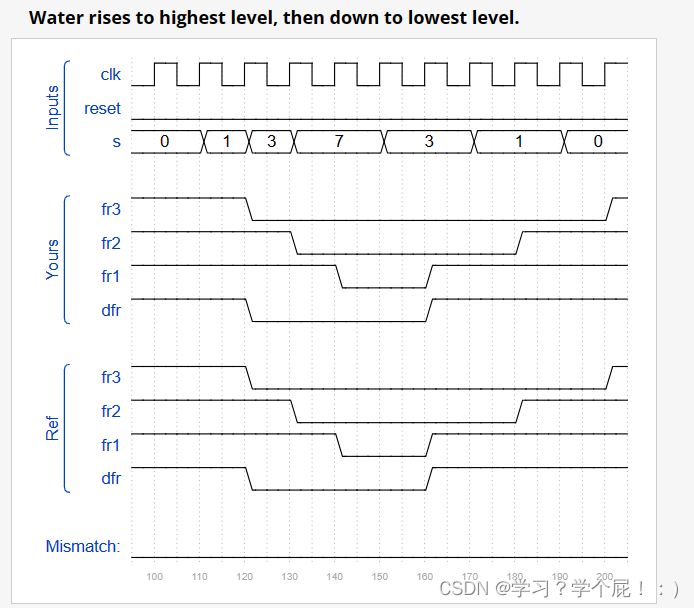

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

reg [2:0] state;

reg [2:0] next_state;

reg [2:0] fr;

parameter LOW_S1=1,LOW_S2=2,LOW_S3=3,HIGH_S3=4;

assign {fr3,fr2,fr1}=fr;

always@(*)begin

next_state=LOW_S1;

case(s)

3'b000:

next_state=LOW_S1;

3'b001:

next_state=LOW_S2;

3'b011:

next_state=LOW_S3;

3'b111:

next_state=HIGH_S3;

endcase

end

always@(posedge clk)

begin

if(reset)begin

state<=LOW_S1;

end

else begin

state<=next_state;

end

end

always@(posedge clk)begin

if(reset)

dfr<=1;

else if(state>next_state)

dfr<=1;

else if(state<next_state)

dfr<=0;

else

dfr<=dfr;

end

always@(posedge clk)begin

if(reset)

fr<=3'b111;

else begin

case(next_state)

LOW_S1:fr<=3'b111;

LOW_S2:fr<=3'b011;

LOW_S3:fr<=3'b001;

HIGH_S3:fr<=3'b000;

endcase

end

end

endmodule

388

388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?