module top_module(

input clk,

input in,

input reset, // Synchronous reset

output [7:0] out_byte,

output done

); //

reg [4:0]state,next_state;

parameter IDLE=4'b0001,START=4'b0010,WAIT=4'b0100,STOP=4'b1000;

reg [3:0]cnt;

always@(*)begin

case(state)

IDLE:

if(in)

next_state<= IDLE;

else

next_state<= START;

START:

begin

if(cnt==4'b1000)

if(in)

next_state<=STOP;

else

next_state<=WAIT;

else

next_state<=START;

end

WAIT:

if(in)

next_state<=IDLE;

else

next_state<=WAIT;

STOP:

if(in)

next_state<=IDLE;

else

next_state<= START;

endcase

end

always@(posedge clk)

if(reset)

cnt<=0;

else if(state==START)

cnt<=cnt+1;

else if(state==START)

cnt<=cnt;

else

cnt<=0;

always@(posedge clk)

if(reset)

state<=IDLE;

else

state=next_state;

assign done=state==STOP;

always@(posedge clk)

if(reset)

out_byte<=8'b0000_0000;

else if(cnt<4'b1000)

out_byte[cnt]<=in;

else

out_byte<=out_byte;

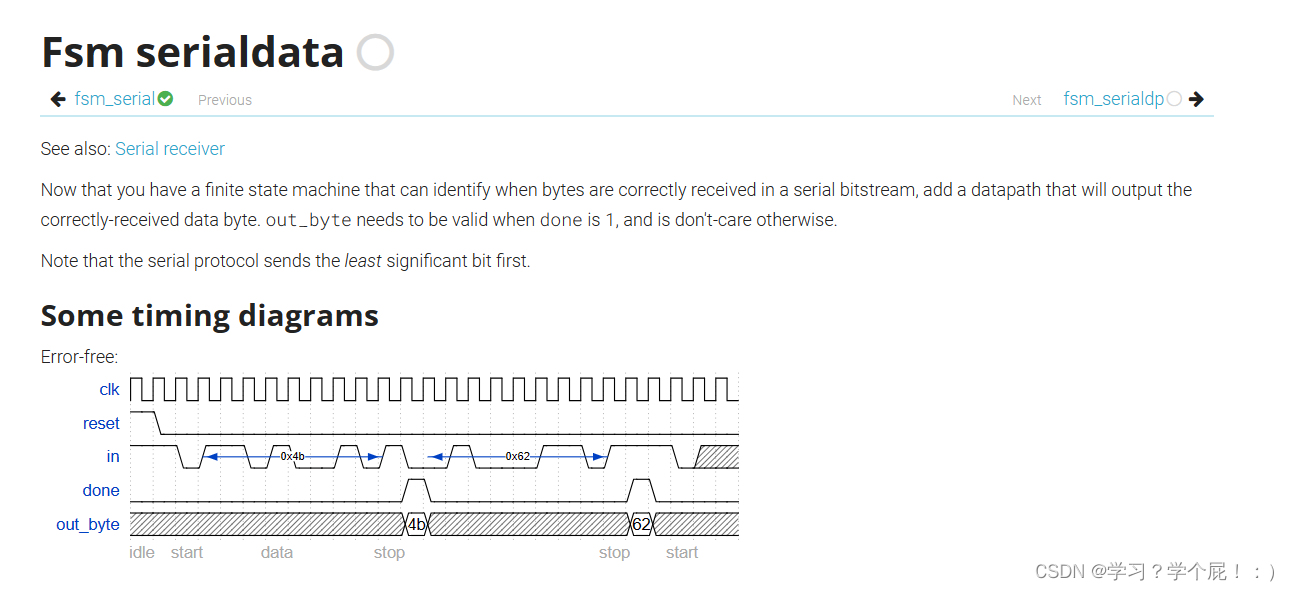

// Use FSM from Fsm_serial

// New: Datapath to latch input bits.

endmodule

494

494

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?