目录

4.2.1 Combinational circuit 1(Sim/circuit1)

4.2.2 Combinational circuit 2(Sim/circuit2)

4.2.3 Combinational circuit 3(Sim/circuit3)

4.2.4 Combinational circuit 4(Sim/circuit4)

4.2.5 Combinational circuit 5(Sim/circuit5)

4.2.6 Combinational circuit 6(Sim/circuit6)

4.2.7 Sequential circuit 1(Sim/circuit7)

4.2.8 Sequential circuit 2(Sim/circuit8)

4.2.9 Sequential circuit 3(Sim/circuit9)

4.2.10 Sequential circuit 4(Sim/circuit10)

前言

HDLbits网站如下

Problem sets - HDLBits (01xz.net)

从本期开始我们继续HDLbits第四章Circuits的学习,本期的内容是Build a circuit from a simulation waveform(4.2.1-4.2.10)

4.2.1 Combinational circuit 1(Sim/circuit1)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input a,

input b,

output q );//

assign q = a&b;

endmodule

4.2.2 Combinational circuit 2(Sim/circuit2)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = ~(a^b^c^d); // Fix me

endmodule

偶数个0对应的输出为1,即为同或

4.2.3 Combinational circuit 3(Sim/circuit3)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = a&c | a&d | b&c | b&d; // Fix me

endmodule

4.2.4 Combinational circuit 4(Sim/circuit4)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b|c; // Fix me

endmodule

4.2.5 Combinational circuit 5(Sim/circuit5)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always@(*) begin

case(c)

0:q=b;

1:q=e;

2:q=a;

3:q=d;

default:q=4'hf;

endcase

end

endmodule

4.2.6 Combinational circuit 6(Sim/circuit6)

这是一个组合电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input [2:0] a,

output [15:0] q );

always@(*) begin

case(a)

0:q=16'h1232;

1:q=16'haee0;

2:q=16'h27d4;

3:q=16'h5a0e;

4:q=16'h2066;

5:q=16'h64ce;

6:q=16'hc526;

7:q=16'h2f19;

endcase

end

endmodule

4.2.7 Sequential circuit 1(Sim/circuit7)

这是一个时序电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input clk,

input a,

output q );

always@(posedge clk) begin

q<=~a;

end

endmodule

4.2.8 Sequential circuit 2(Sim/circuit8)

这是一个时序电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input clock,

input a,

output p,

output q );

always@(*) begin

if(clock)

p=a;

end

always@(negedge clock) begin

q<=p;

end

endmodule

4.2.9 Sequential circuit 3(Sim/circuit9)

这是一个时序电路。读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input clk,

input a,

output [3:0] q );

always@(posedge clk) begin

if(a)

q<=4;

else if(q<6)

q<=q+1;

else

q<=0;

end

endmodule

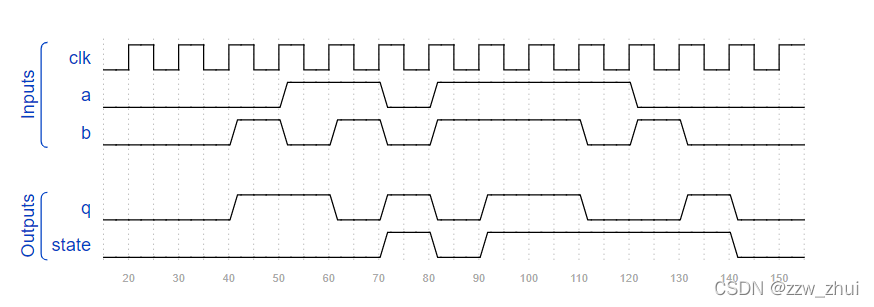

4.2.10 Sequential circuit 4(Sim/circuit10)

这是一个时序电路。该电路由组合逻辑和一位存储器(即一个触发器)组成。触发器的输出通过输出状态是可观察的。

读取仿真波形,确定电路的功能,然后实现。

Solution:

module top_module (

input clk,

input a,

input b,

output q,

output state );

always@(posedge clk) begin

state<=a&b|a&state|b&state;

end

assign q=a^b^state;

endmodule

通过时序图观察到,q不仅与a、b有关,还与state有关。next_state也与a、b、state有关。

只不过q是即时的所以是组合assign赋值,next_state慢了一个周期,所以是时序always赋值

快结束啦

1619

1619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?