2.2.6Vector concatenation operater

问题陈述:

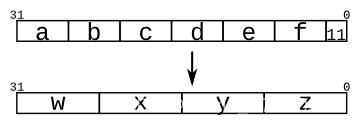

给定几个输入向量,将它们连接在一起,然后将它们分成几个输出向量。有六个 5 位输入向量:a、b、c、d、e 和 f,总共 30 位输入。有四个 8 位输出向量:w、x、y 和 z,用于 32 位输出。输出应该是输入向量的串联,后跟两个1位:

verilog代码:

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign {w,x,y,z}={a,b,c,d,e,f,2'b11};

endmodule

2.2.7 Vector reversal 1

问题陈述:

给定一个 8 位输入向量 [7:0],反转其位顺序。

Verilog代码:

module top_module(

input [7:0] in,

output [7:0] out

);

assign {out[0],out[1],out[2],out[3],out[4],out[5],out[6],out[7]}=in;

endmodule

2.2.8 Replication operator

问题陈述:

构建一个将 8 位数字符号扩展为 32 位的电路。这需要连接 24 个符号位副本(即复制位 [7] 24 次),然后是 8 位数字本身。

Verilog 代码:

module top_module (

input [7:0] in,

output [31:0] out );//

assign out={{24{in[7]}},in};

endmodule

2.2.9 More replication

问题陈述:

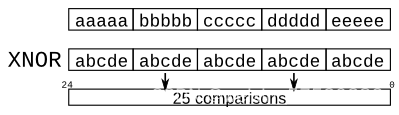

给定五个 1 位信号(a、b、c、d 和 e),计算 25 位输出向量中的所有 25 个成对的一位比较。如果被比较的两位相等,则输出应为 1。

out[24] = ~a ^ a; // a == a, so out[24] is always 1.

out[23] = ~a ^ b;

out[22] = ~a ^ c;

…

out[ 1] = ~e ^ d;

out[ 0] = ~e ^ e;

如图所示,使用复制和连接运算符可以更轻松地完成此操作。顶部向量是每个输入的 5 次重复的串联

底部向量是 5 个输入的串联的 5 次重复

Verilog代码:

module top_module (

input a, b, c, d, e,

output [24:0] out );

wire [24:0] top,bottom;

assign top={{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}};

assign bottom={5{a,b,c,d,e}};

assign out=~top^bottom;

endmodule

每日总结

1.位拼接运算符{}:可以把两个或多个信号的某些位拼接起来进行运算操作。

其使用方法如下:

{信号1的某几位,信号2的某几位…信号n的某几位}

1)在为表达式中不允许存在没有指明位数的信号,这是因为在计算拼接信号位宽的大小时必须知道其中每个信号的位宽。

2)位拼接可以用重复法来简化表达式,其表示方法如下:

{num{向量}}

这是将向量复制num次。num必须是个常数。

64

64

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?