Xilinx FPGA一路时钟输入两个PLL

实现方法:

1、时钟为全局时钟输入引脚输入。

2、输入时钟首先进入IBUFG + BUFG,然后输出一个全局时钟

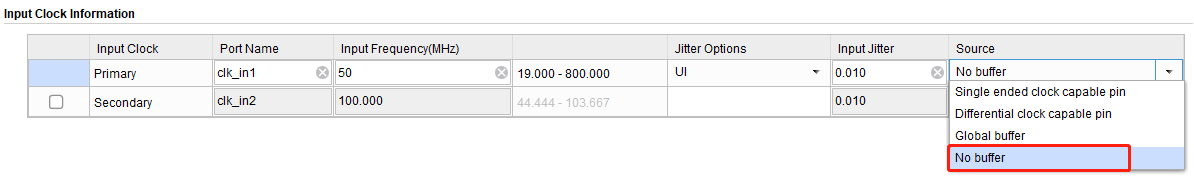

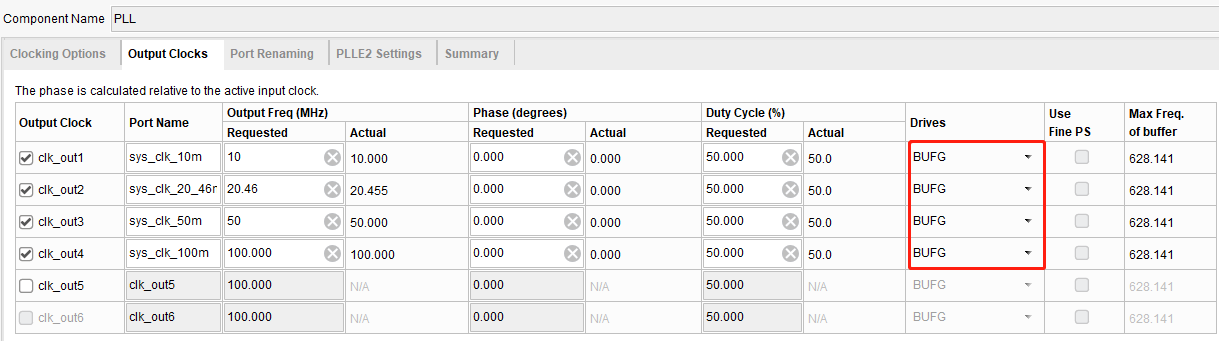

3、将输出的全局时钟分别输入两个PLL,PLL配置输入为No Buffer,输出为BUFG/BUFGCE等

代码如下:

wire O ;

IBUFG IBUFG_inst (

.O(O), // Buffer output

.I(i_sys_clk_50m) // Buffer input (connect directly to top-level port)

);

wire O1;

BUFG BUFG_inst(

.O(O1), // 1-bit output: Clock output

.I(O) // 1-bit input: Clock input

);

PLL PLL_INST(

// Clock out ports

.sys_clk_10m ( )

,.sys_clk_20_46m ( )

,.sys_clk_50m ( )

,.sys_clk_100m ( )

// Status and control signals

,.reset ( 0 )

,.sys_rst_n ( sys_rst_n )

// Clock in ports

,.clk_in1 ( O1 )

);

wire clk_10m ;

wire clk_100m ;

wire clk_50m1 ;

wire clk_50m2 ;

wire clk_50m3 ;

wire clk_50m4 ;

wire rst_n1 ;

wire clk_10m_ce ;

wire clk_100m_ce ;

wire clk_50m1_ce ;

wire clk_50m2_ce ;

wire clk_50m3_ce ;

wire clk_50m4_ce ;

reg [15:0] cnt111;

reg flag111;

wire w_flag ;

assign w_flag = flag111 ;

// assign clk_100m_ce = flag111 ?

clk_wiz_1 clk_wiz_1_inst(

// Clock out ports

.clk_10m_ce(1),

.clk_10m(sys_clk_10m),

.clk_100m_ce(rst_n1),

.clk_100m(sys_clk_100m),

.clk_50m1_ce(1),//

.clk_50m1(sys_clk_50m),

.clk_50m2_ce(flag111),

.clk_50m2(clk_50m2),

.clk_50m3_ce(flag111),

.clk_50m3(clk_50m3),

.clk_50m4_ce(flag111),

.clk_50m4(clk_50m4),

// Status and control signals

.reset(0),

.locked(rst_n1),

// Clock in ports

.clk_in1(O1)

);

1257

1257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?