门控时钟主要有两种电路:锁存门控和寄存门控

锁存门控(ASIC往往做成了标准库单元):

最常用的门控时钟电路,面积小,做成标准库单元后时序可控。

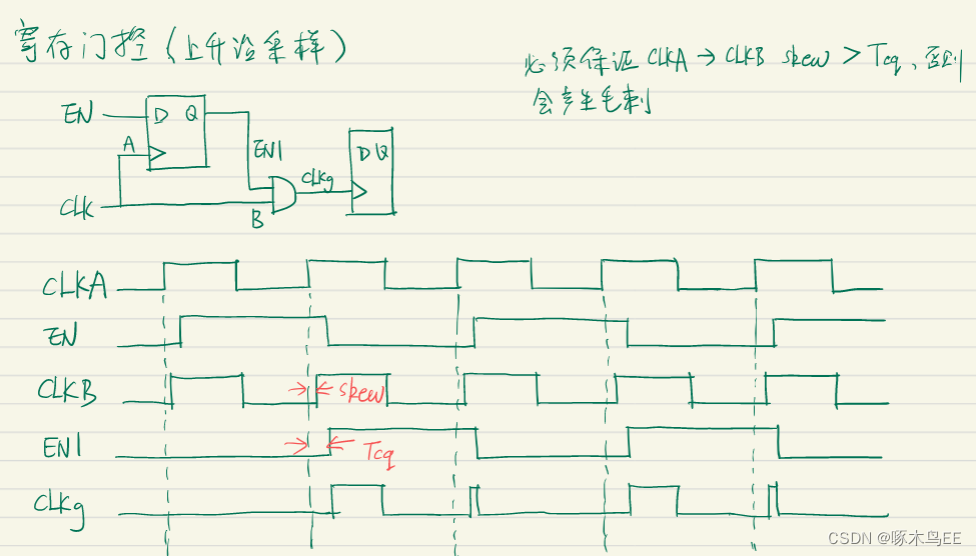

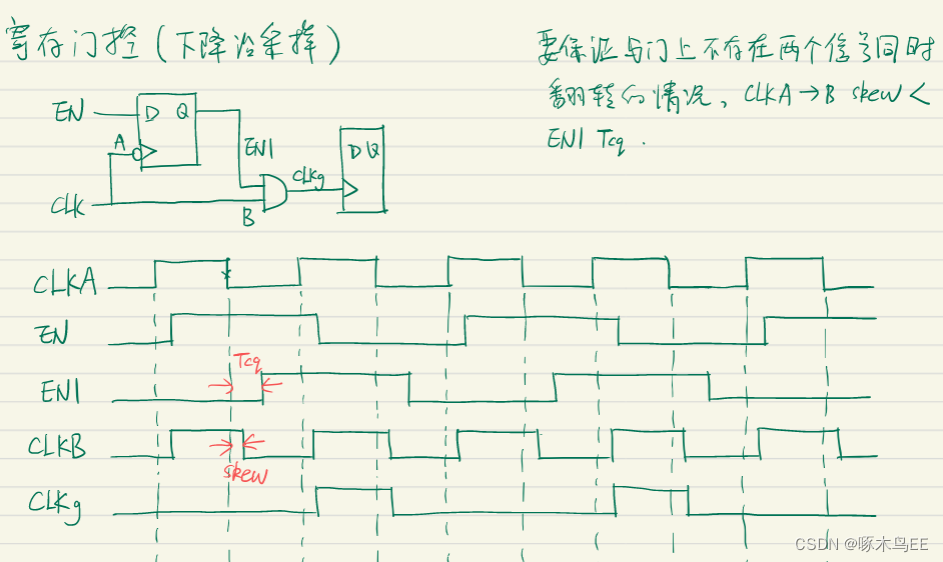

寄存门控:

1)上升沿采样:必须保证CLKA -> CLKB的skew > Tcq,否则会产生毛刺。但真实的ASIC CTS都会尽量做clock balance,如果这个地方要求skew必须大于一定的值,会人为引入clock delay,可能导致其他没有CG的path产生时序问题。所以这种设计并不好。

2)下降沿采样:比起上升沿采样显然更合理了,对CTS友好。但是面积比锁存器要大,所以也不常用。

5471

5471

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?