名称:在7段数码管上显示自己的最后三位学号数字Verilog代码Vivado仿真(文末获取)

软件:Vivado

语言:Verilog

代码功能:

在7段数码管上显示自己的最后三位学号数字

1.实验任务

要求将自己的最后三位学号数字在数码管上显示2、实验现象与结果

应能看见自己学号稳定的在数码管上显示,并用手机拍摄记录下来。3、实验报告

(1)简单陈述在数码管上显示数字的原理。

(2)画出编写 Verilog程序的功能框图。

(3)说明改变扫描频率的软件方法,及对显示的影响。

(4)附上 Verilog实验源程序,并对关键或重要的程序语句给出简要的注释和说明。

(5)将显示的学号截图附上。

(6)如果调试过程遇到了问题,应将问题截图,并给出解决问题的办法和对应的截图

1. 学号显示

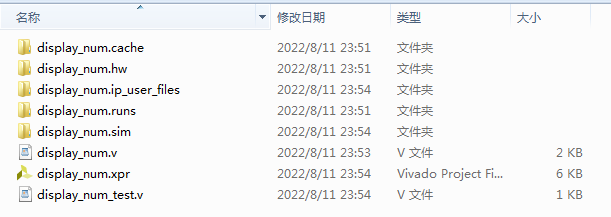

工程文件

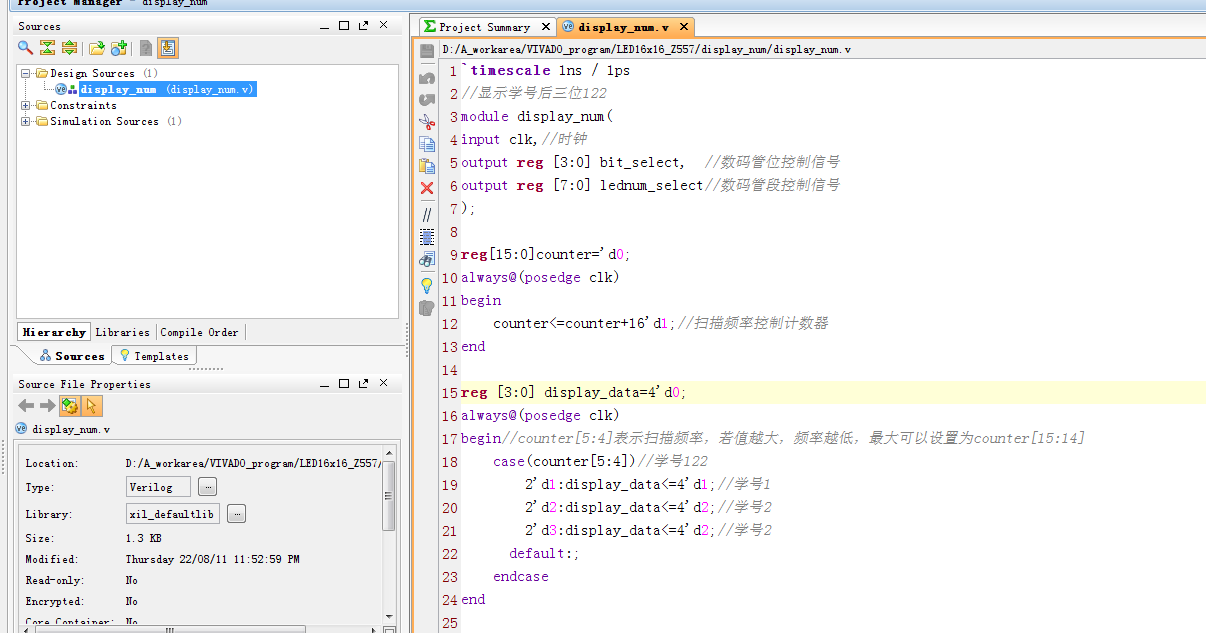

程序文件

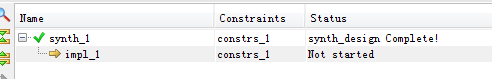

程序编译

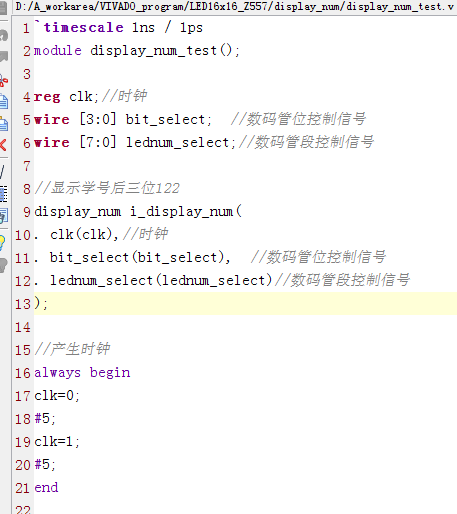

Testbench

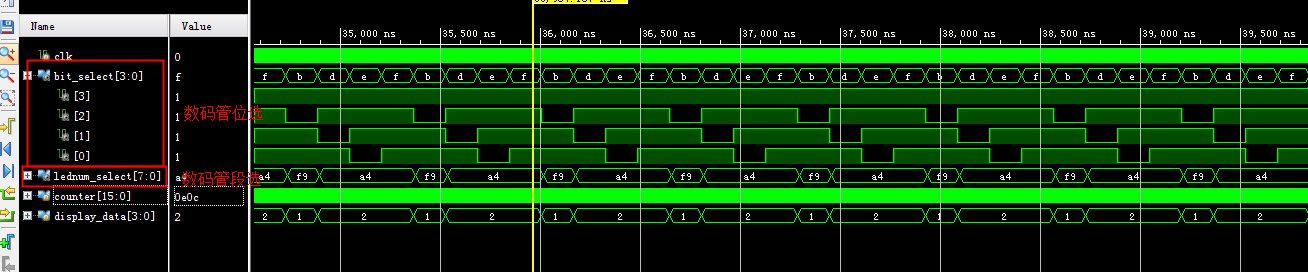

仿真图

部分代码展示:

`timescale 1ns / 1ps //显示学号后三位122 module display_num( input clk,//时钟 output reg [3:0] bit_select, //数码管位控制信号 output reg [7:0] lednum_select//数码管段控制信号 ); reg[15:0]counter='d0; always@(posedge clk) begin counter<=counter+16'd1;//扫描频率控制计数器 end reg [3:0] display_data=4'd0; always@(posedge clk) begin//counter[5:4]表示扫描频率,若值越大,频率越低,最大可以设置为counter[15:14] case(counter[5:4])//学号122 2'd1:display_data<=4'd1;//学号1 2'd2:display_data<=4'd2;//学号2 2'd3:display_data<=4'd2;//学号2 default:; endcase end always@(posedge clk) begin//counter[5:4]表示扫描频率,若值越大,频率越低,最大可以设置为counter[15:14] case(counter[5:4])//数码管位控制信号低电平有效 2'd1: bit_select<=4'b1011;//显示第1个数码管 2'd2: bit_select<=4'b1101;//显示第2个数码管 2'd3: bit_select<=4'b1110;//显示第3个数码管 default:bit_select<=4'b1111;//不显示 endcase case(display_data)//数码管段控制信号低电平有效 0 : lednum_select= 8'hc0; //显示0 1 : lednum_select= 8'hf9; //显示1 2 : lednum_select= 8'ha4; //显示2 3 : lednum_select= 8'hb0; //显示3 4 : lednum_select= 8'h99; //显示4 5 : lednum_select= 8'h92; //显示5 6 : lednum_select= 8'h82; //显示6 7 : lednum_select= 8'hf8; //显示7 8 : lednum_select= 8'h80; //显示8 9 : lednum_select= 8'h90; //显示9 endcase end endmodule

源代码

扫描文章末尾的公众号二维码

7324

7324

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?