名称:74LS194电路设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

(限定 Quartus ll完成)用VHDL设计19

4,再用VHDL层次结构设计方法设计程序实现

图示电路并仿真,底层器件是194。层次化设计,分模块调试。

1. 工程文件

2. 程序文件

完整电路代码

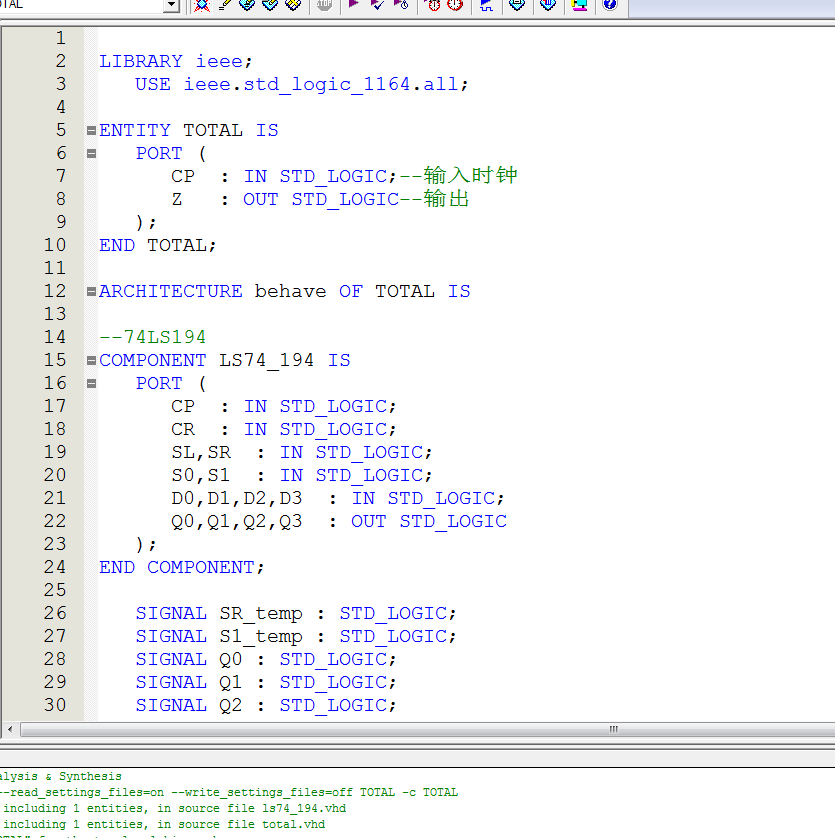

底层74LS194器件代码

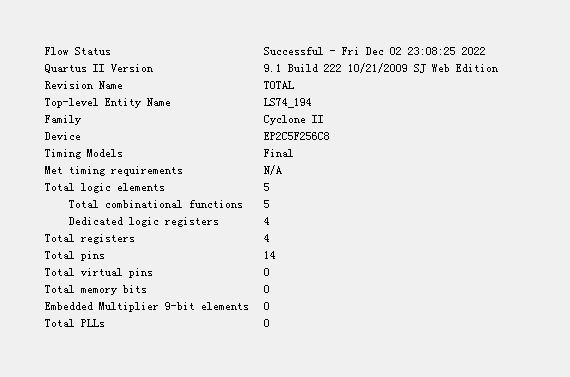

3. 程序编译

整体统计报告

底层74LS194器件统计报告

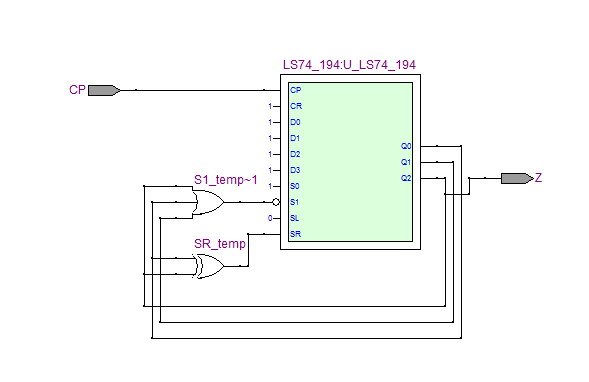

4. RTL图

5. 仿真图

整体仿真图

74LS194模块仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --74LS194 ENTITY LS74_194 IS PORT ( CP : IN STD_LOGIC; CR : IN STD_LOGIC; SL,SR : IN STD_LOGIC; S0,S1 : IN STD_LOGIC; D0,D1,D2,D3 : IN STD_LOGIC; Q0,Q1,Q2,Q3 : OUT STD_LOGIC ); END LS74_194; ARCHITECTURE behave OF LS74_194 IS SIGNAL Q0123 : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN PROCESS (CP, CR) BEGIN IF (CR = '0') THEN Q0123 <= "0000"; ELSIF (CP'EVENT AND CP = '1') THEN IF(S1='0' and S0='0')THEN--保持 Q0123 <= Q0123; ELSIF(S1='0' and S0='1')THEN--右移 Q0123(3) <= SR;

源代码

扫描文章末尾的公众号二维码

1938

1938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?