名称:QPSK调制解调器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

QPSK调制解调器设计

1、调制信号通过外部信号控制

2、将调制信号进行QPSK调制,并将调制后的波形通过DAC转换为模拟信号输出

3、接收模拟QPSK信号,通过ADC转换为数字信号

4、对转换后是数字信号进行QPSK解调,输出2bit解调后的数据

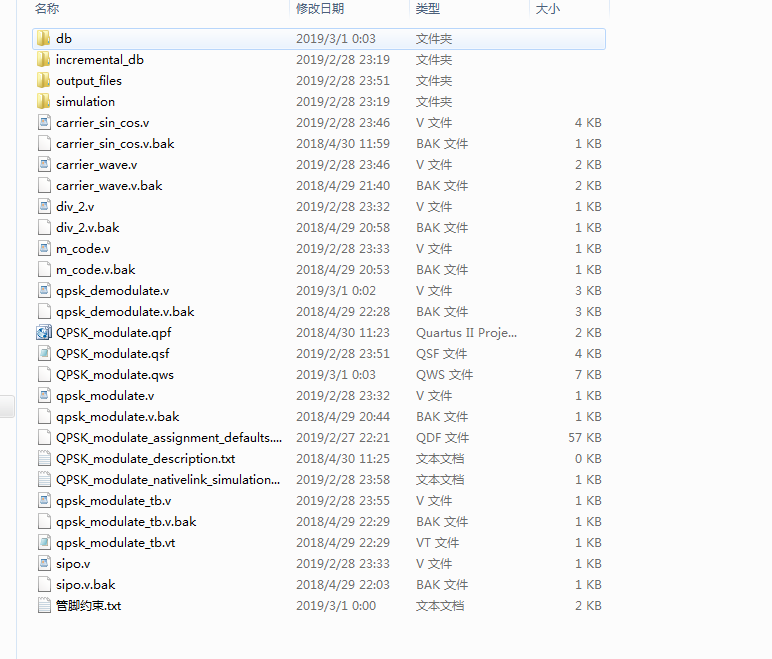

1. 工程文件

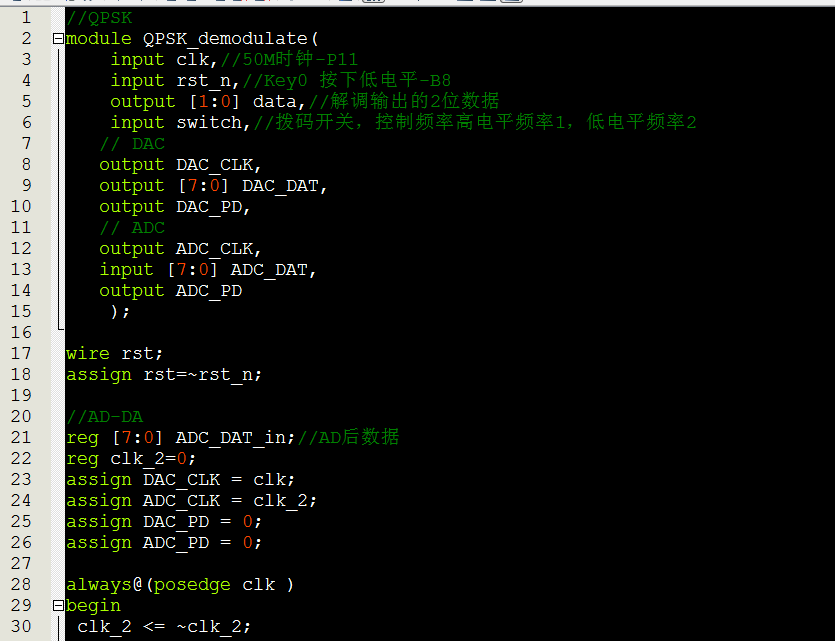

2. 程序文件

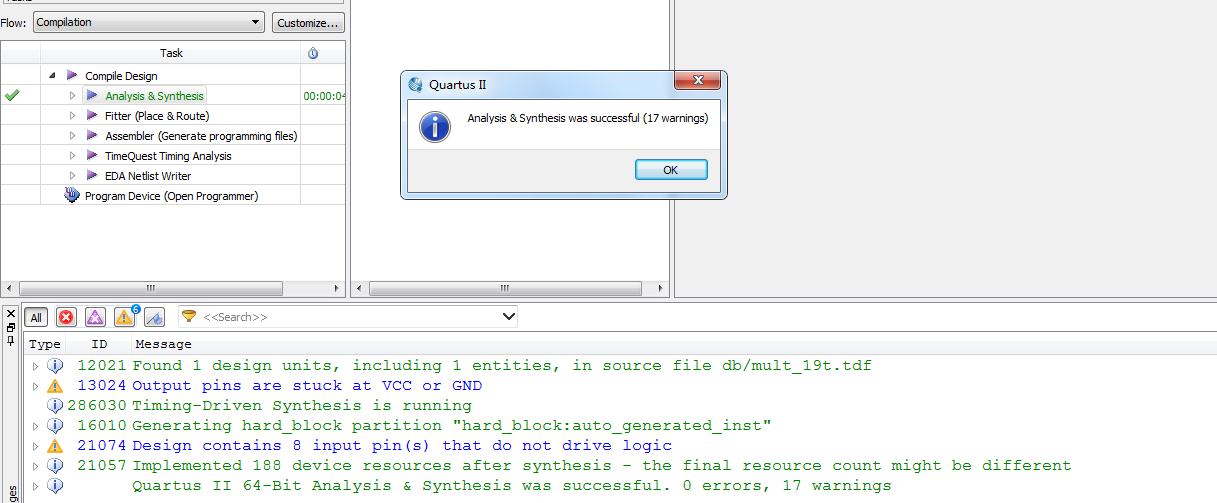

3. 程序运行

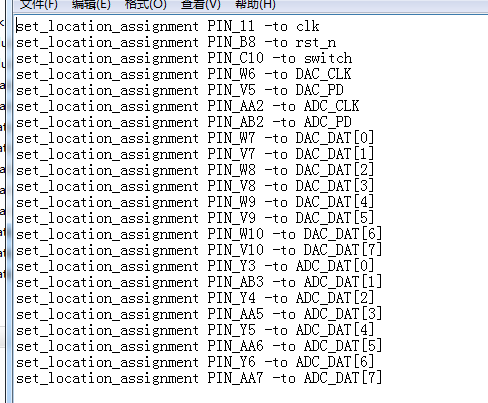

4. 管脚约束

5. 仿真图

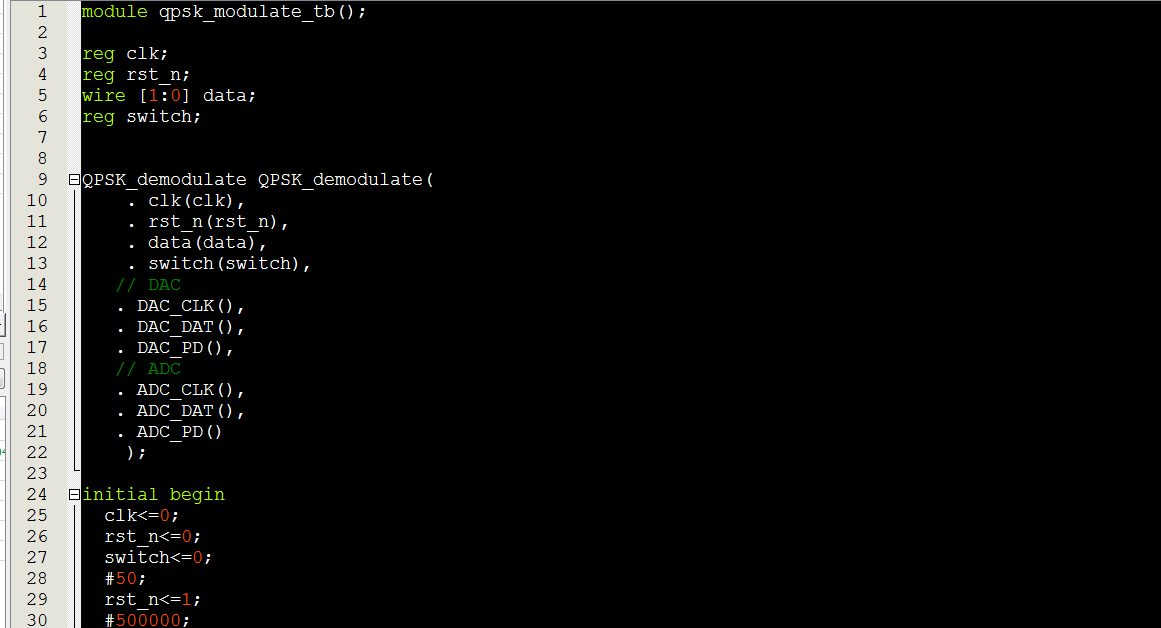

Testbench

仿真图

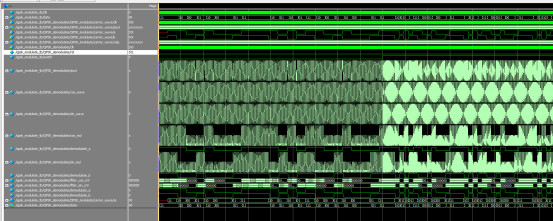

整体仿真图

整体仿真图放大

Switch(开关)信号控制两种频率

Sin 、cos两个相互正交的载波信号

输出的QPSK调制信号

![]()

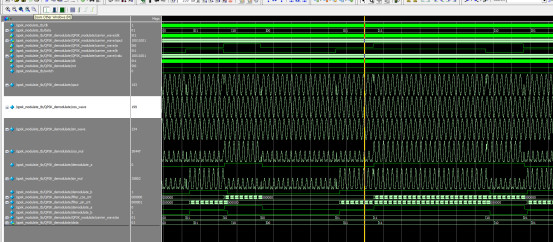

解调时,载波与调制信号相乘后波形

解调得a,b信号,组成2bit的data信号,图中ss为原始信号,可看出data等于ss,解调正确

![]()

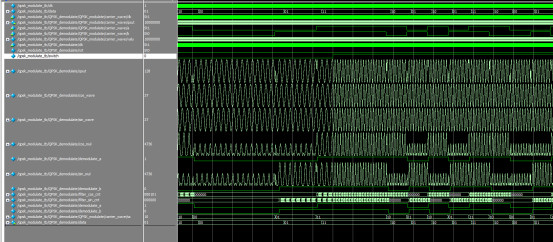

开关切换频率

部分代码展示:

//QPSK module QPSK_demodulate( input clk,//50M时钟-P11 input rst_n,//Key0 按下低电平-B8 output [1:0] data,//解调输出的2位数据 input switch,//拨码开关,控制频率高电平频率1,低电平频率2 // DAC output DAC_CLK, output [7:0] DAC_DAT, output DAC_PD, // ADC output ADC_CLK, input [7:0] ADC_DAT, output ADC_PD ); wire rst; assign rst=~rst_n; //AD-DA reg [7:0] ADC_DAT_in;//AD后数据 reg clk_2=0; assign DAC_CLK = clk; assign ADC_CLK = clk_2; assign DAC_PD = 0; assign ADC_PD = 0; always@(posedge clk ) begin clk_2 <= ~clk_2; end always @(posedge clk) begin ADC_DAT_in <= ADC_DAT; end wire [7:0] qout; wire [7:0] cos_wave; wire [7:0] sin_wave; assign DAC_DAT=qout;//输出调制波形 wire clk_ctrl; assign clk_ctrl=switch? clk:clk_2;//通过控制时钟来控制频率 //QPSK调制模块 QPSK_modulate QPSK_modulate( . clk(clk_ctrl), . rst(rst), . qout(qout) ); //正交载波模块 carrier_sin_cos carrier_sin_cos( . clk(clk_ctrl), . rst(rst), . cos_wave(cos_wave), . sin_wave(sin_wave) ); wire [16:0] cos_mul; wire [16:0] sin_mul; //载波相乘.仿真用该句 assign cos_mul=cos_wave*qout;//*ADC_DAT assign sin_mul=sin_wave*qout;

源代码

点击下方的公众号卡片获取

3210

3210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?