1、组合逻辑为多周期延迟时

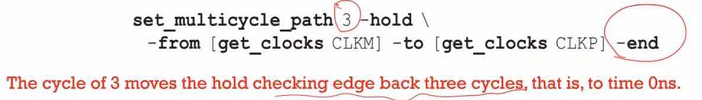

一般默认的hold的capture edge是setup capture edge的前一个上升沿。

2、组合逻辑为半周期延迟时

一般电路中setup非常好修,hold特别难修。因此采用半周期路径比较好,setup比较紧,hold特别松。

3、set_false_path命令中,使用through时会使得静态时序分析变得复杂,因此尽量少使用。

set_false_path -from[get_clocks clockA]-to [get_clocks clockB]相较于set_false_path -from[get_pins{regA_}/CP]-to[get_pins{regB_}/D]会更快。

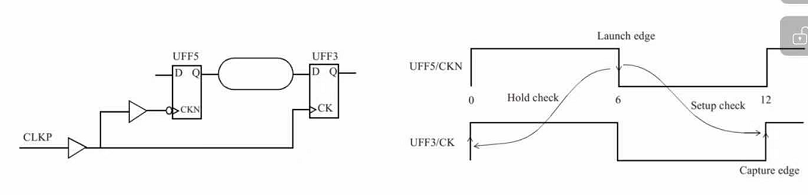

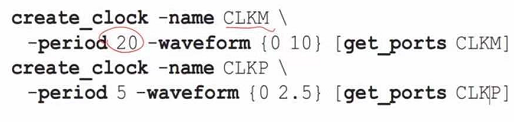

4、多时钟-slow to fast

5、多时钟-fast to slow

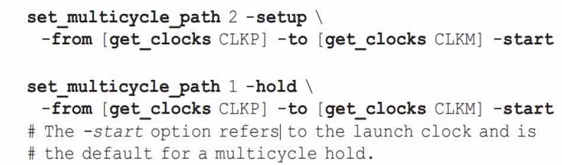

6、多时钟

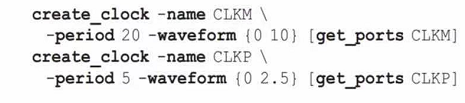

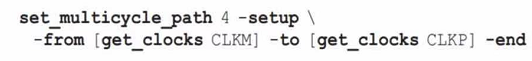

CLKP时钟域为数据发送路径,CLKM时钟域为数据捕捉路径,找到最严苛的两个时钟上升沿进行分析setup.

CLKM时钟域为数据发送路径,CLKP时钟域为数据捕捉路径,找到最严苛的两个时钟上升沿进行分析setup.

当时钟之间有相移

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?