现代多层布线工艺:

宽厚和间距大的连线布置在高层,M5及以上采用较厚连线,全局连线和电源线;墨迹和较薄的连线布置在底层,包括局部单位内连线。

导线:

集成电路的导线已经形成复杂的几何形状,会引起电容、电阻和电感等寄生参数效应,使得传播延时增加,影响功率和能耗的分布,会引起额外的噪声,对电路的性能和电路的可靠性均有影响。

ELMORE延时模型

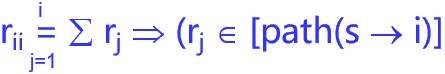

路径电阻:从源节点到任何节点之间存在唯一的电阻路径,其总电阻称为路径电阻。

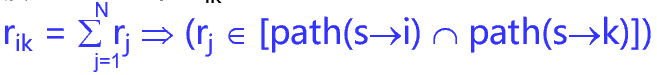

共享路径电阻:表示从输入节点到i及k两个节点的路径中共享部分的总电阻rik。

i节点 的elmore延时为:

i节点 的elmore延时为:

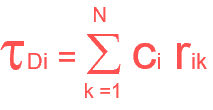

导线的分布式RC模型

导线长度为L,分割成N段,每段电阻r L/N,每段的电容 c L/N

利用Elmore延时计算

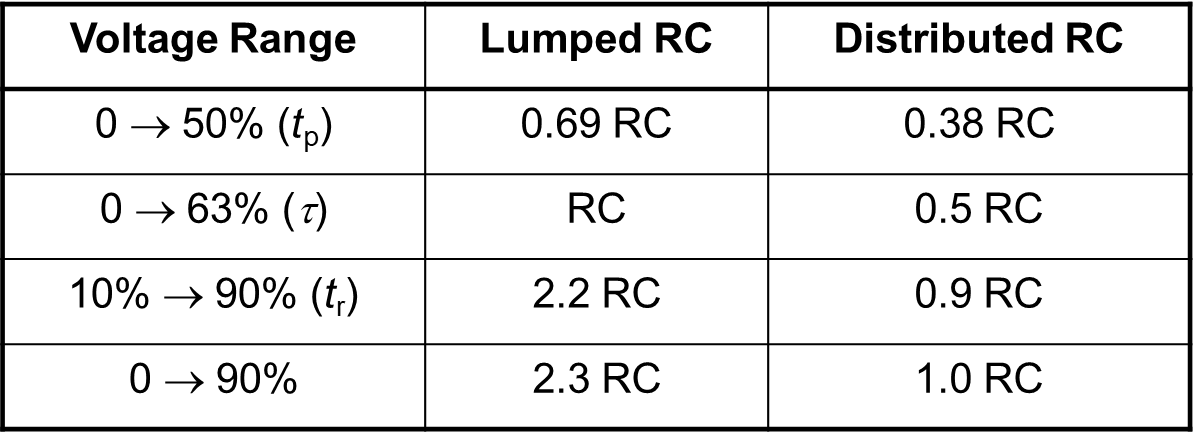

集总RC模型和分布RC模型的阶跃响应

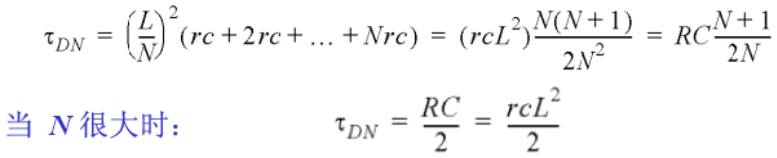

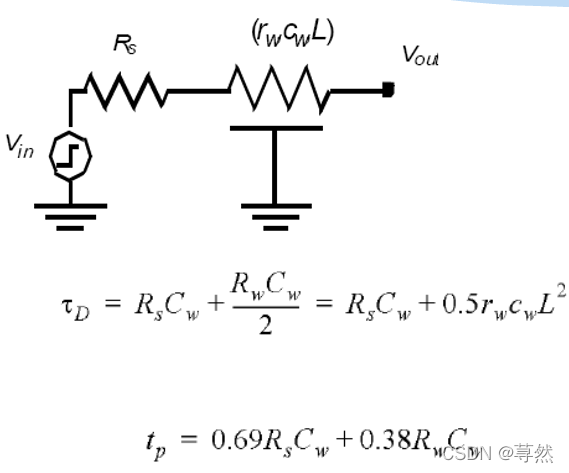

考虑驱动器内阻RS时RC线的延时

考虑驱动器内阻RS时RC线的延时

数字集成电路(第二章)导线与传输线模型

最新推荐文章于 2025-02-20 11:59:48 发布

现代集成电路布线工艺中,宽厚连线通常位于高层,而底层则用于精细布线。导线的几何形状影响电容、电阻和电感,导致传播延迟、功率消耗和噪声问题。Elmore延时模型被用来计算路径电阻和延迟,同时考虑了分布式和集总RC模型对信号的影响。这些因素对电路性能和可靠性至关重要。

现代集成电路布线工艺中,宽厚连线通常位于高层,而底层则用于精细布线。导线的几何形状影响电容、电阻和电感,导致传播延迟、功率消耗和噪声问题。Elmore延时模型被用来计算路径电阻和延迟,同时考虑了分布式和集总RC模型对信号的影响。这些因素对电路性能和可靠性至关重要。

3548

3548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?