一、基础知识

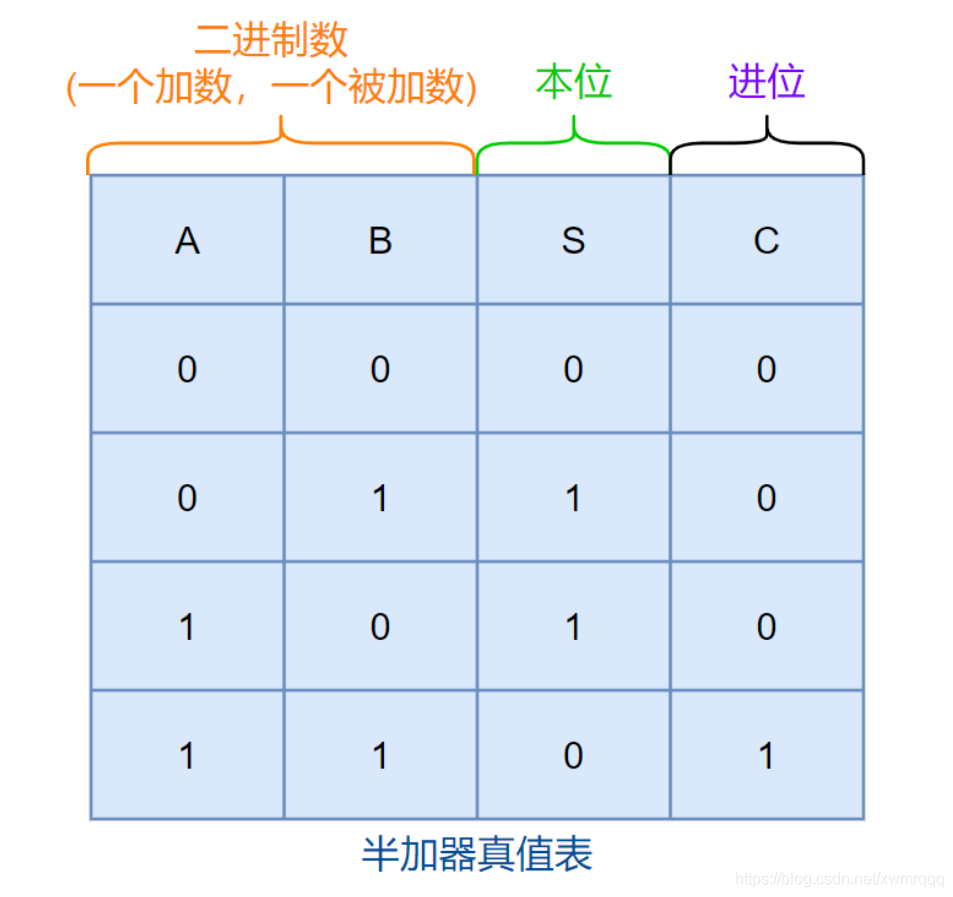

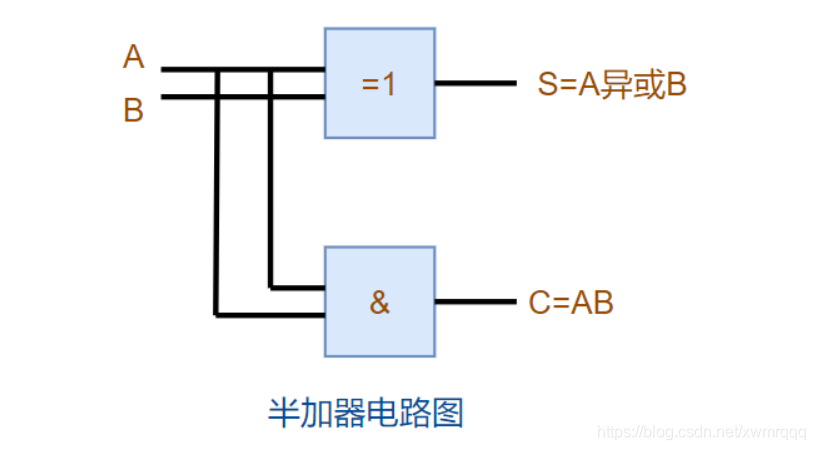

1. 半加器

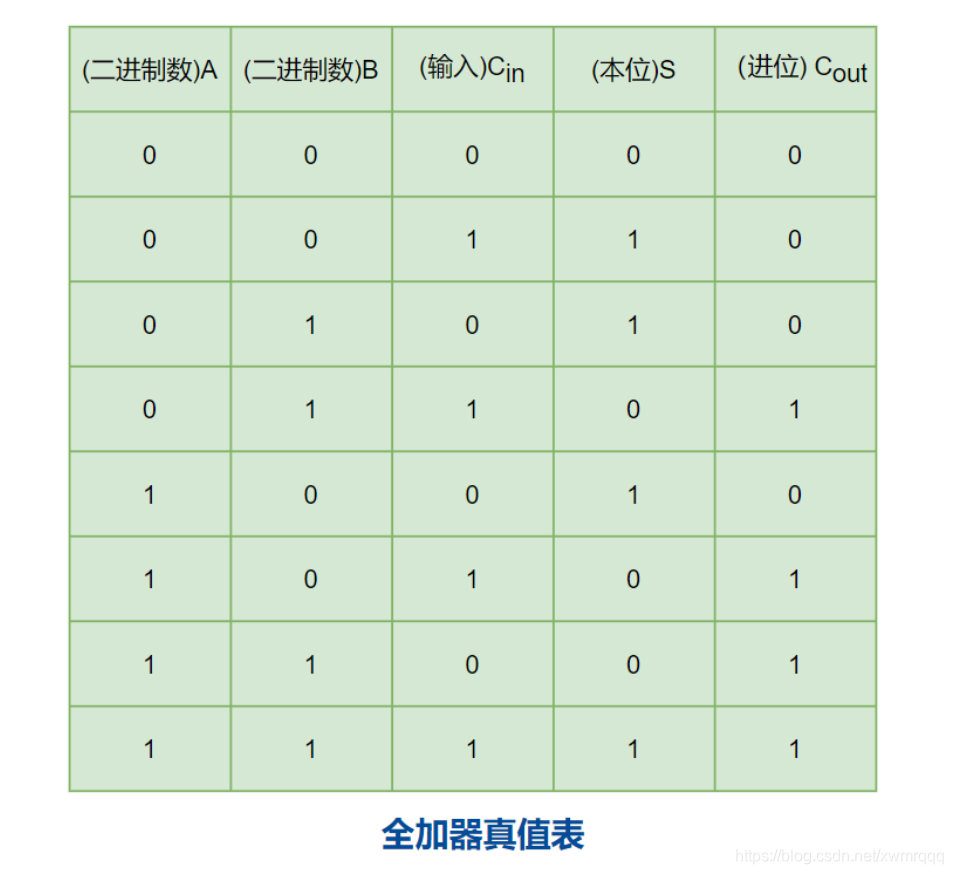

2. 全加器

二、原理图实现1位全加器

软件基于quartusII 13.0版本,开发板基于Intel DE2-115quartusII 软件的一些基本用法请参考:Quartus-II实现D触发器的三种方式

1. 新建工程

文件取名如下:

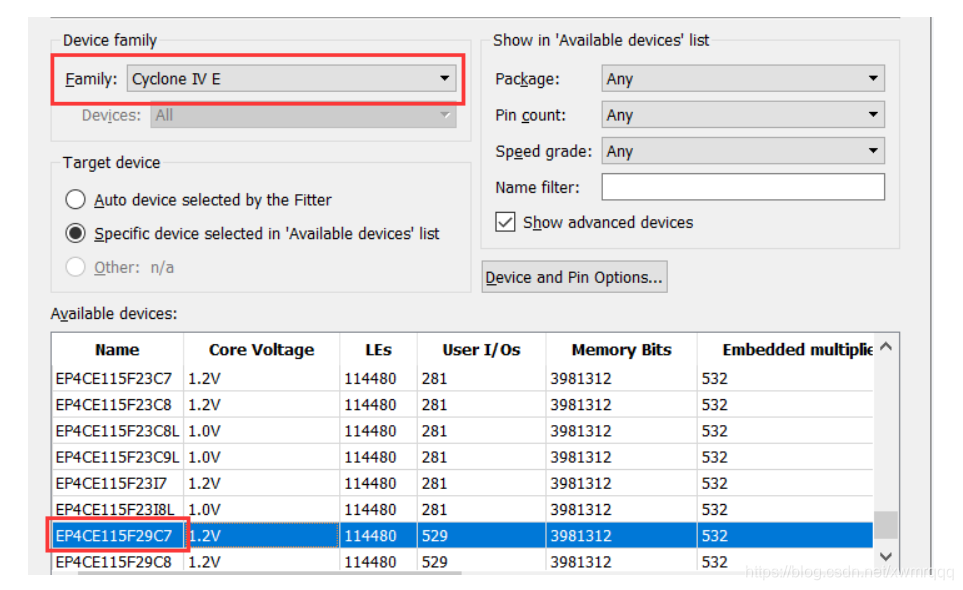

芯片型号选择如下:

2. 新建半加器原理图文件

打开QuartusII,选菜单“File”一“New”,在弹 出的“New-”对话框中选择“ Design Files” 的原理图文件编辑输入项 “Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

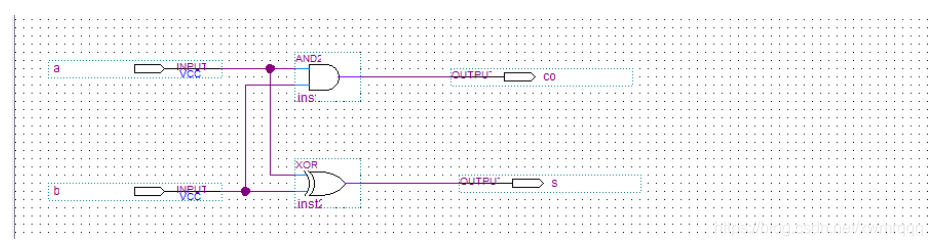

分别调入元件and2, xor,然后设计原理图如下:

保存该文件为:half_adder.bdf,然后进行编译

3. 将设计项目设置成可调用的元件

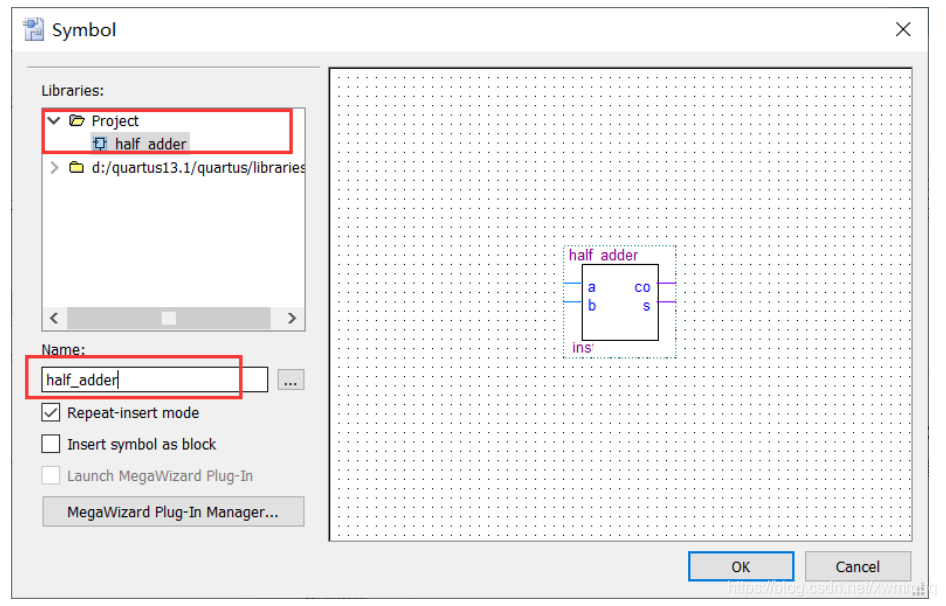

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf 设置成可调用的元件。

选择菜中File中的Create/Update→Create Symbol Files for Current File项,即可将当前文件half_adder. bdf变成一个元件符号存盘,以 待在高层次设计中调用。

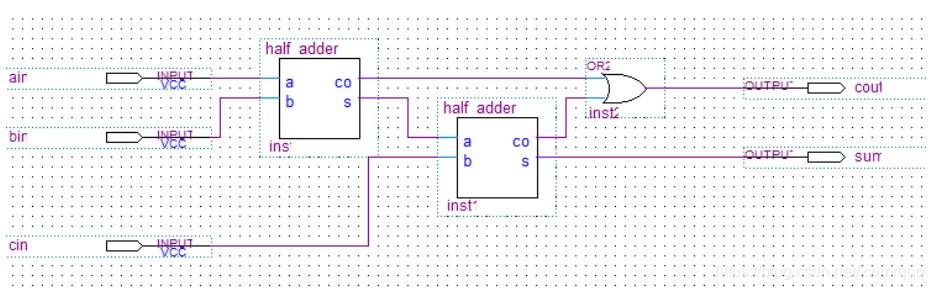

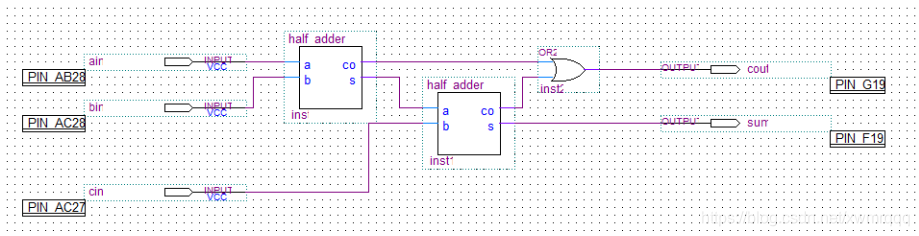

4. 新家全加器原理图文件

新建方法同第二步新建半加器原理图文件方法一样

在弹出的“symbol”窗的“name”栏输入底层文件半加器的存储名“half_adder” 调出半加器

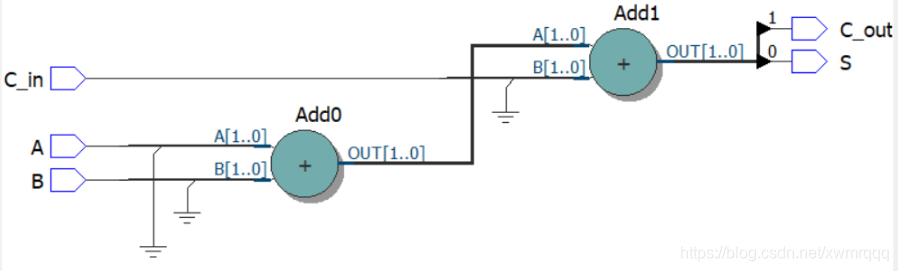

然后设计原理图如下:

5. 将设计项目设置成顶层文件并编译仿真

将顶层文件full_adder.bdf设置为顶层文件的方法:选中full_adder.bdf文件,然后project→set as top_level entity。

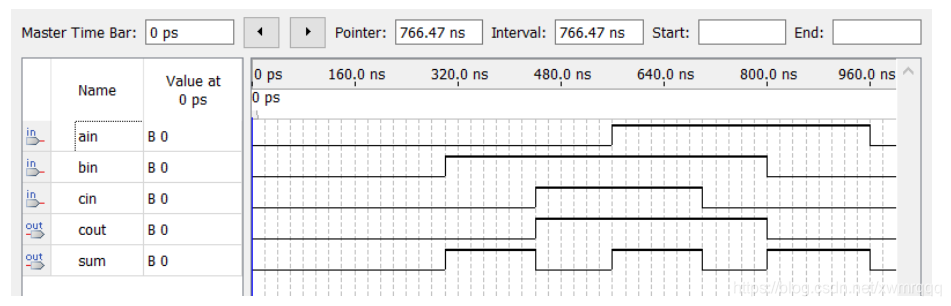

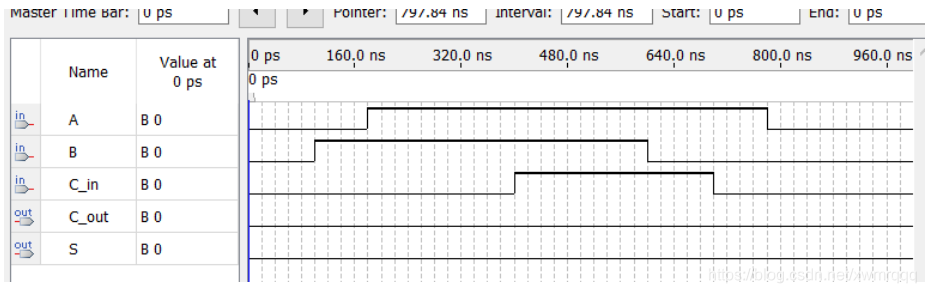

仿真前:

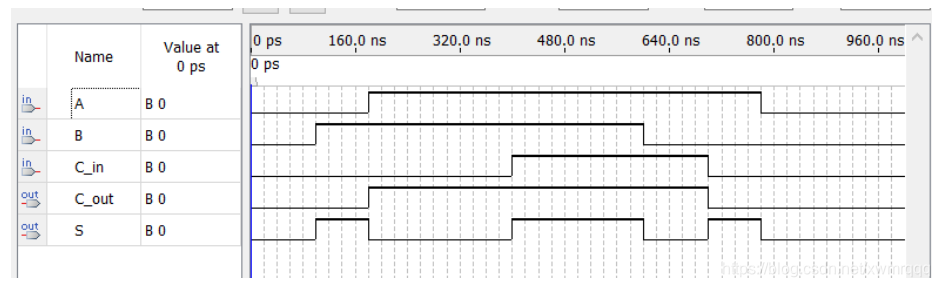

仿真后:

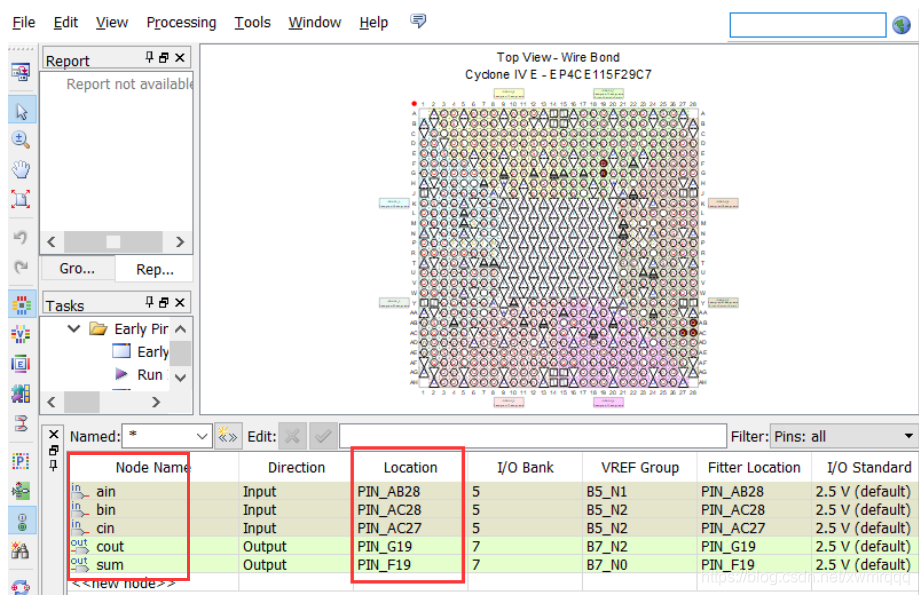

6. 引脚绑定及硬件下载测试

① 选择目标芯片:cycloneIVE系列的EP4CE11529C7 ,在菜单中选择,“assignments→device…”(同新建工程所选择的型号一样)

② 引脚绑定

先从菜单中选择“assignments→pin planner”,然后进行如下配置:

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上

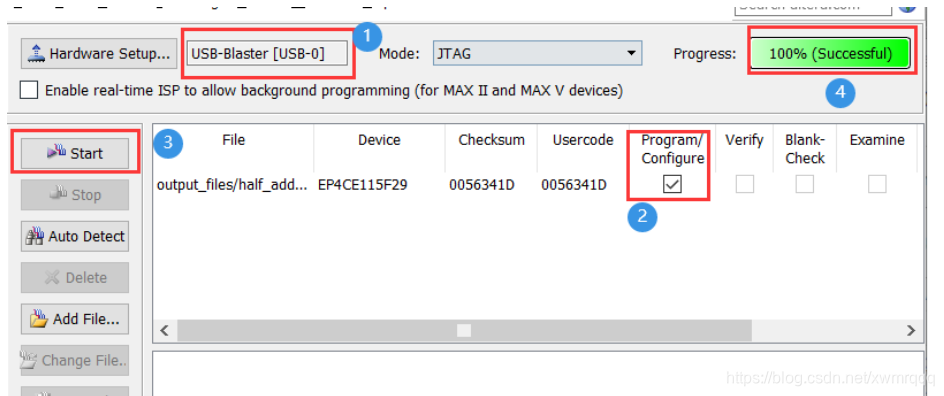

③ 把开发板接上电源,USB 接口接电脑, 然后点击Programmer按钮,然后弹出一个下载界面。

如果第一次下载需安装 硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USB blaster”,再点击“ok”,则硬件被安装上。

如果找不到,请先在电脑设备管理器中配置USB-Blaster驱动

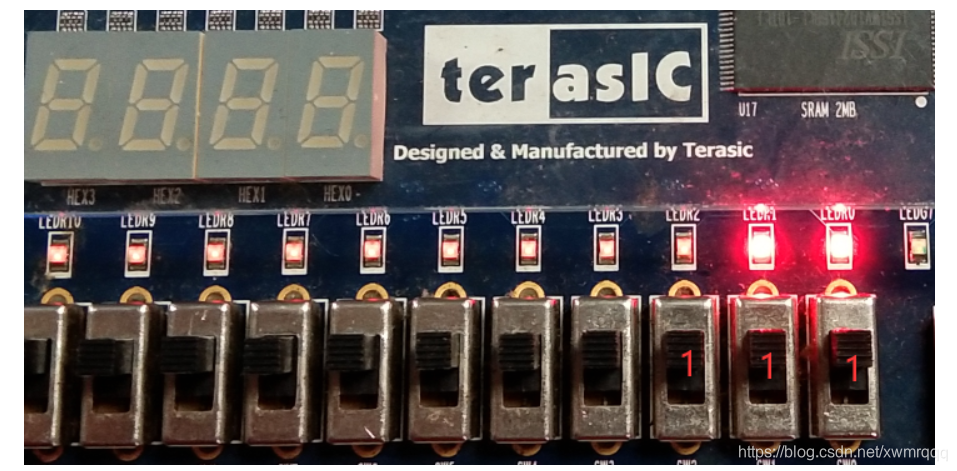

④ 板子显示结果

三、Verilog实现1位全加器

1. 新建工程

工程名字为add_1bit,芯片型号选择同上

2. 新建一个Verilog文件

File -----> New -----> Verilog HDL File

内容如下:

module add_1bit(S,C_out,A,B,C_in);

input A,B,C_in ;

output S,C_out ;

reg S,C_out ;

always @(A or B or C_in)

begin

{C_out,S} = A +B +C_in ;

end

endmodule

从抽象层次来说,这并不是用数电的设计方法来实现的,但是这不影响我们通过这个来实现一位全加器。

该Verilog文件名为 add_1bit.v

编译之后,查看其硬件电路图如下:

3. 开始仿真

仿真前:

仿真后:

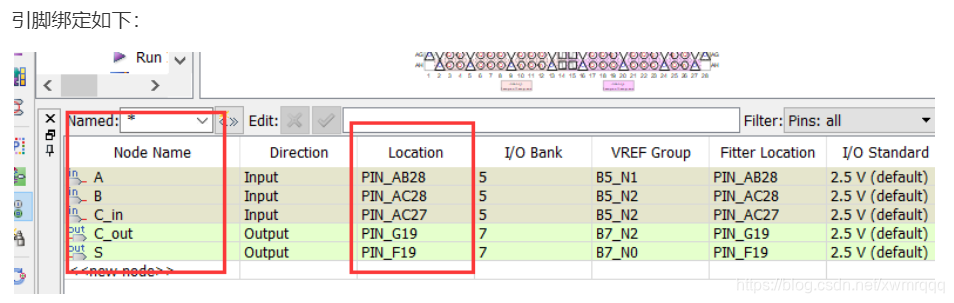

4. 引脚绑定及硬件下载测试

步骤同原理图实现1位全加器第⑥步一样

引脚绑定如下:

下载结果:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-17cg2olI-1617791734637)(E:%5Cdasan2%5C%E5%AE%9E%E9%AA%8C%E4%BD%9C%E4%B8%9A%5C%E5%B5%8C%E5%85%A5%E5%BC%8F%E7%B3%BB%E7%BB%9F%E5%BA%94%E7%94%A8%E5%BC%80%E5%8F%91%5CFPGA%20%E5%AE%9E%E7%8E%B0%E4%B8%80%E4%BD%8D%E5%85%A8%E5%8A%A0%E5%99%A8%E8%AE%BE%E8%AE%A1%5C1617791251576.png)]](https://i-blog.csdnimg.cn/blog_migrate/4145c5dd39d3fd2d813b52ed37b8b452.png)

板子显示结果:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-q7qSfEuQ-1617791734638)(E:%5Cdasan2%5C%E5%AE%9E%E9%AA%8C%E4%BD%9C%E4%B8%9A%5C%E5%B5%8C%E5%85%A5%E5%BC%8F%E7%B3%BB%E7%BB%9F%E5%BA%94%E7%94%A8%E5%BC%80%E5%8F%91%5CFPGA%20%E5%AE%9E%E7%8E%B0%E4%B8%80%E4%BD%8D%E5%85%A8%E5%8A%A0%E5%99%A8%E8%AE%BE%E8%AE%A1%5C1617791613544.png)]](https://i-blog.csdnimg.cn/blog_migrate/82221dd5a6f89f39d32ba18e1fe27be0.png)

1069

1069

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?