文章目录

一、问题描述

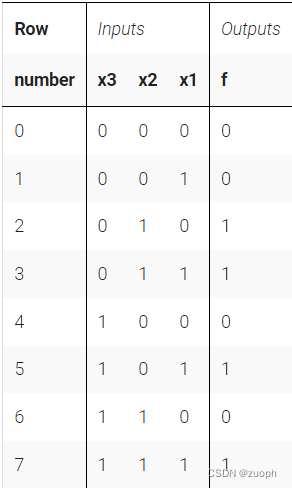

本节我们学习用真值表来描述组合逻辑的行为,通过真值表我们将组合逻辑的每一种输入和输出对应值都罗列出来。

对于一个N个输入的布尔函数,理论上有2的N次方输入组合。下表是一个3输入的例子。

假设现在我们来设计电路实现上表描述的功能,并且限定我们只能使用标准的逻辑门电路比如与门、或门等。我们该如何创建这个组合逻辑电路呢?

一种简单的方法是我们使用积之和来描述,积意味着与门,和意味着或门。从表中我们可以发现行2、3、5及7的输出为1,这样我们可以写出输出的积之和形式的逻辑表达式。

f=(~x3&x2& ~x1) | ( ~x3&x2&x1) | ( x3& ~x2 & x1) | ( x3&x2&x1)

二、verilog源码

module top_module(

input x3,

input x2,

input x1, // three inputs

output f

订阅专栏 解锁全文

订阅专栏 解锁全文

44

44

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?