目录

一、前言

在FPGA设计中,最常提到的一个词就是时序,而与之相关最不想看到的就是时序违例。

那什么是时序违例?在工程设计中的单元可分为组合逻辑单元和时序逻辑单元,两者的区别是看是否需要时钟信号,如LUT的输入全为数据信号,不需要时钟,就是组合逻辑单元,像FF,ROM等需要有时钟信号输入的就是时序逻辑单元。

对于时序单元,因为输入同时有数据信号和时钟信号,此时为保证输出的信号准确,就说时钟信号和数据信号到达输入端口的先后顺序有要求,这个要求是很矫情的,数据信号要比时钟的采集边沿提前到达,但有不能提前太多。如果不满足这个要求时序单元的输出可能就会异常,这种情况即是时序违例。

二、时序违例的确认

如何知道时序是否违例?FPGA设计工具如Vivado会有对应的时序报告,查看报告可以知道是否存在违例路径。

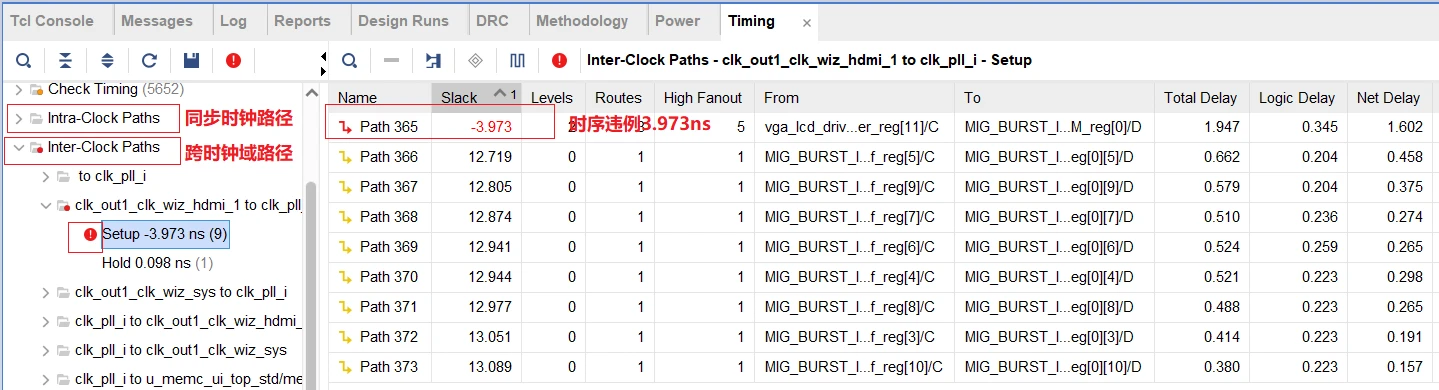

报告查看包括同步时钟路径(intra-clock paths)与跨时钟域路径(inter-clock paths)的时序,如果路径的slack为负数,则对应的路径前会标红色告警符号,如下图中跨时钟域路径中出现了时序违例的路径。

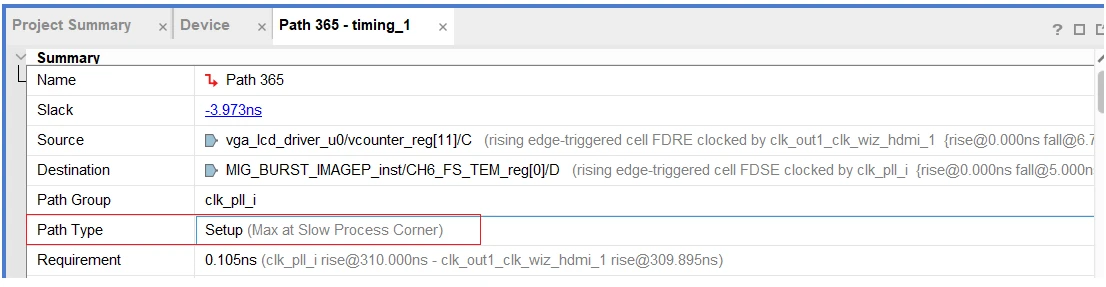

根据不同工艺,以及时序分析类型,违例可分为slow corner下的setup/hold/recovery/removal和fast corner下setup/hold/recovery/removal共8种类型的违例,具体路径属于哪一类,可以点击路径查看Path Type,如上图的违例为slow corner下的setup违例

三、时序违例的影响

a)、逻辑功能问题

时序违例可能导致FPGA设计运行时出现逻辑功能错误,即设计的输出结果与预期出现不一致,为什么说是可能?因为在违例的情况下,违例路径单元上的输出有可能正确,也可能不正确,即是一种不确定状态。

b)、性能问题

时序违例会导致设计达不到预期的最高频率

c)、可靠性问题

如果频繁地出现时序违例,因不断地处于临界状态,增加电路原件的应力,从而导致器件老化,不仅使用寿命受影响,可靠性也将受影响。

d)、不确定性

时序违例使电路中会出现信号冒险,噪声增加,导致出现不确定性。

因此,设计如果出现时序违例,根据时序报告进行优化,使时序满足要求。

266

266

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?