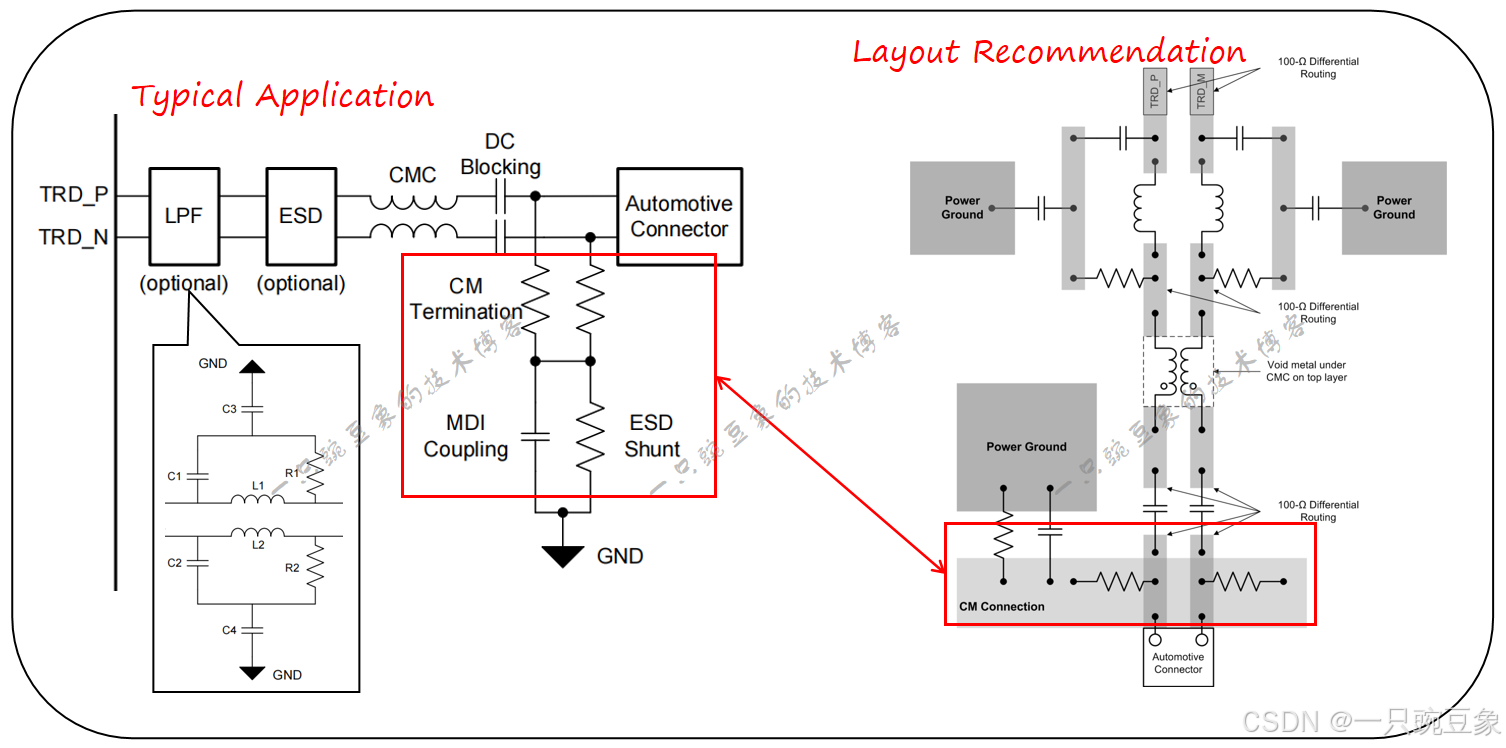

以太网的MDI接口应用中,共模端接网络的应用广泛,并且,其电路参数从100 BASE-T1到1000 BASE-T1保持了相同的参数定义[2][3],这就不得不引起使用者的怀疑,毕竟百兆和千兆以太网的工作频段差异巨大,这样的设计真的可以做到上下兼容吗?本文针对此问题,进行了深入的探讨。

在参考文献[1]中,作者对标准中提出的1000BASE-T1共模终端(CMT)进行了分析,特别是计算了该电路的混合模式S参数,此外,还使用简单的PCB测试板进行了仿真和测量,最终,所得结果显示出很好的一致性,并在此基础上,对CMT进行了评价,结论是,当前的CMT电路设计仅仅在非常有限地程度上减小了共模能量。

为了评估1000 BASE-T1的CMT电路效果,使用了如下图所示的混合S参数模型,考虑CMT的等效电路对任何混合模信号都是对称的,因此,只需要考虑六组不同的参数:Sdd11, Sdd21, Scd11, Scd21, Scc11, Scc21,并以此为基础形成散射参数矩阵,注意,图示省略了中间转换环节(先计算Z1

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4095

4095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?