Modelsim仿真出现 No Design Loaded 怎么办

一、出现的问题

根据上一篇,基于FPGA的双线性插值算法设计与modelsim分析的最后,我们对仿真波形进行了简单的分析,但在加入VGA显示模块后,Modelsim能够自动跳转,但是却没有任何其他波形窗口等跳出。

观察整个界面发现,左下角出现 No Design Loaded ,这是唯一给到的信息。于是去搜索各种解决办法,尝试之后均没有改变。

二、解决办法

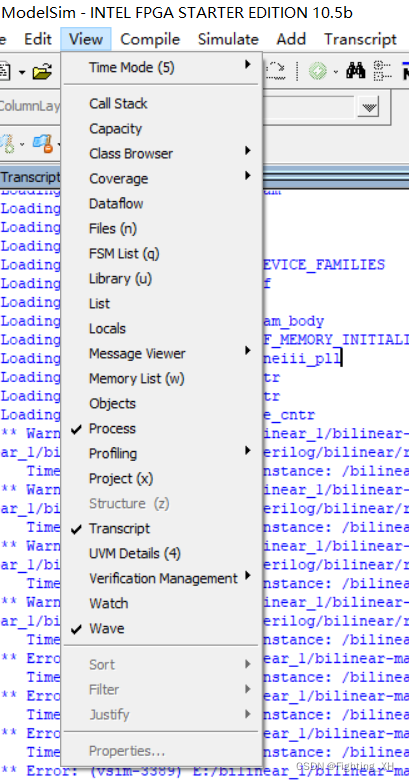

我们要想办法,让仿真软件能给我们提供更多信息,从而去纠错。如下图所示,点击View——transcript,就会出现各种运行记录,其中也会提示Error,就可以根据提示进行修改了。

我当时一直找不到错误的原因,仅仅是不出任何波形,对修改更是无处下手,看提示发现,仅仅是因为module中 多打了一个逗号!!!!不过也算学会了如何让仿真软件去显示更多的仿真信息。

三、modelsim不能自动出现波形

同样的,当quartus中调用modeslim仿真的时候,可能出现无波形的情况,这时候可以采用手动添加等方式,但如果手动添加仍然没有解决该问题,那么我们也要在transcript窗口中找错误,错误修改后,重新仿真即可。

有效参考

644

644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?