文章目录

前言

-

本次学习的最终目的是为了掌握Zynq Soc FPGA,Zynq Soc FPGA和我们之前介绍的intel Soc FPGA的基本架构是一样的,现网上关于Zynq Soc FPGA的资料较多,因此先掌握这一块,从而可以更好的理解intel Soc FPGA。

-

Zynq Soc FPGA 包含PS和PL两部分,其中PS部分是ARM部分,PL是FPGA的部分,这里同样对应着我们intel Soc FPGA 的HPS和FPGA部分。

-

根据之前quartus的FPGA学习经验,这里先掌握PL端的设计流程。于是就由之前的quartus开发FPGA,变成了用Vivado来开发。

-

之前一直用quartus,因此听到Vivado比较恐惧,但是出于资料的原因,不得不接触,但是接触后发现操作流程都是一样的,大概只是界面不同而已,另外Vivado的界面比较复杂,多操作几遍就可以啦。

一、PL部分

- 学习的目的:掌握如何用Vivado进行FPGA设计

- 设计内容:实现一个简单的二选一多路器

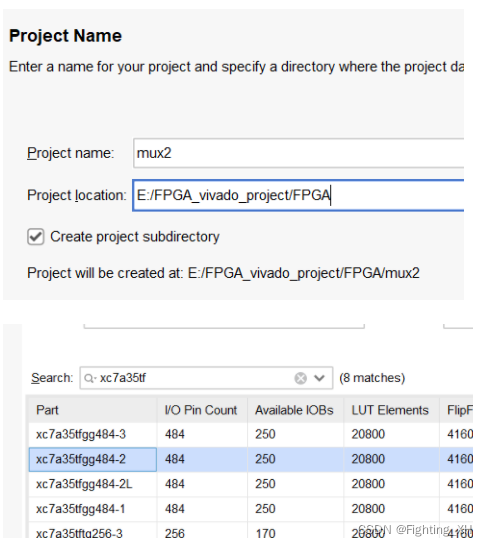

1、创建工程

Create Project—— 填项目名称(注意路径)—— 选择对应器件——finish

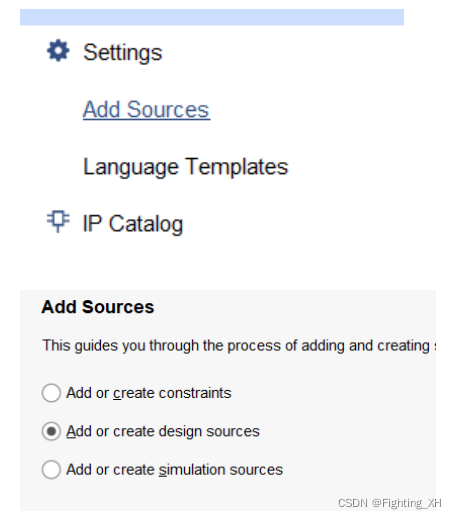

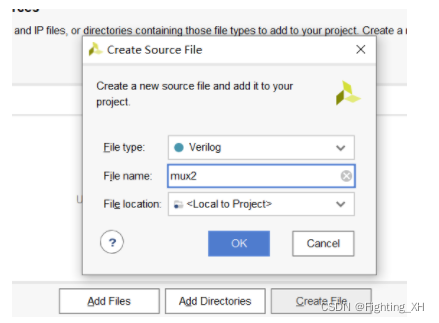

2、添加.V文件

左侧栏找到Add Sources——选择创建HDL文件—— Create File(给出名字)——finish

3、编写程序后分析综合(就是普通的verilog程序)

module mux2(

input a,

input b,

input sel,

output out

);

assign out = (sel == 1 )? a:b;

endmodule

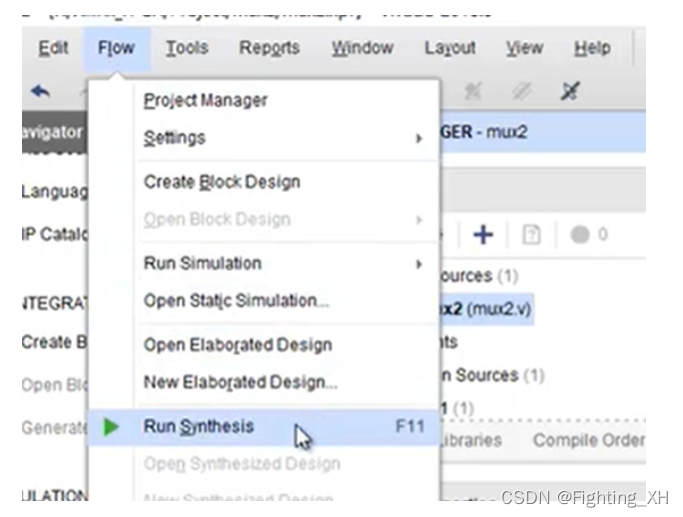

分析和综合

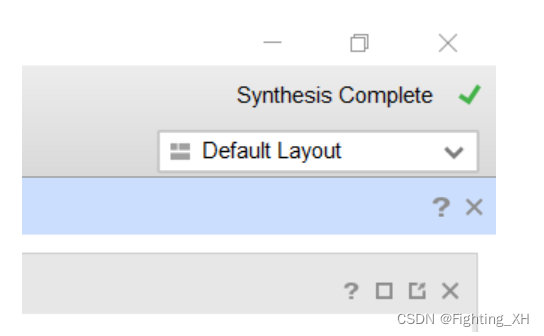

右上角等待分析综合成功

完成之后可显示报告进行查看

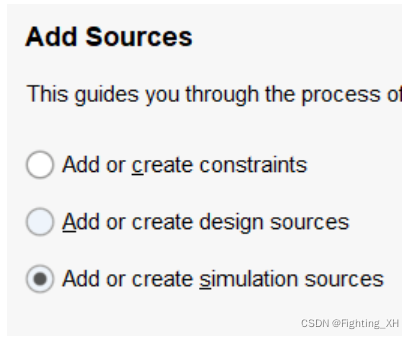

4、编写仿真文件并进行仿真(和上述方法一样,只是在添加文件的时候选择仿真文件即可)

timescale 1ns / 1ns

module mux2_tb( );

reg a;

reg b;

reg sel;

wire out;

mux2 mux2 (

.a(a),

.b(b),

.sel(sel),

.out(out)

);

initial begin

a = 0;b = 0; sel = 0;

#200;

a = 0;b = 1; sel = 0;

#200;

a = 0;b = 1; sel = 1;

#200;

a = 1;b = 1; sel = 0;

#200;

$stop;

end

endmodule

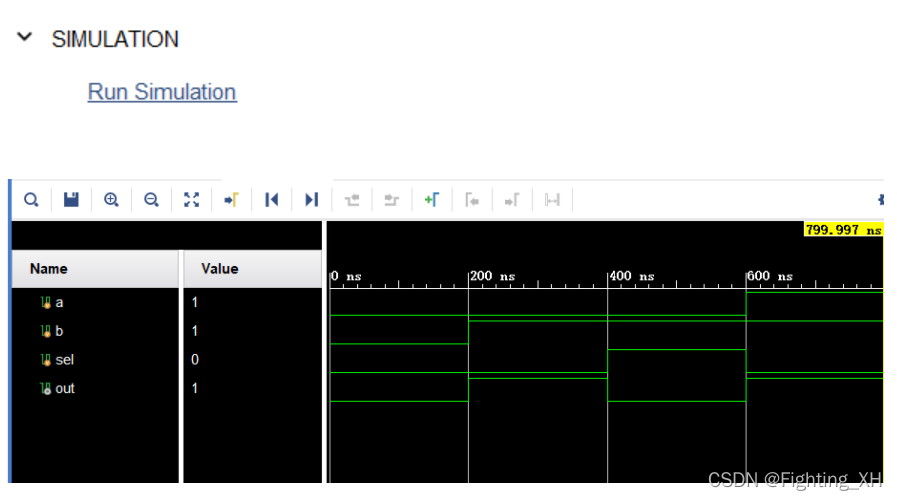

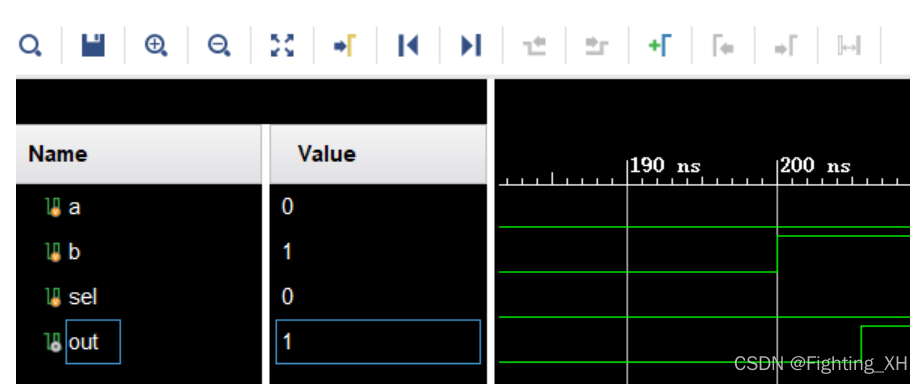

编写完成后,即可运行仿真

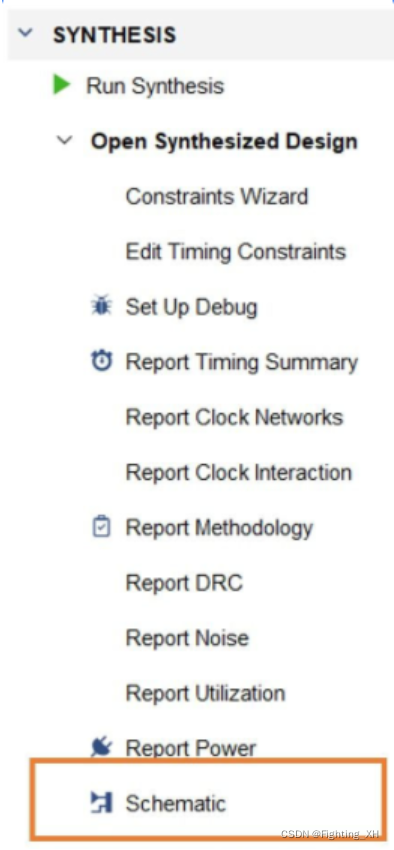

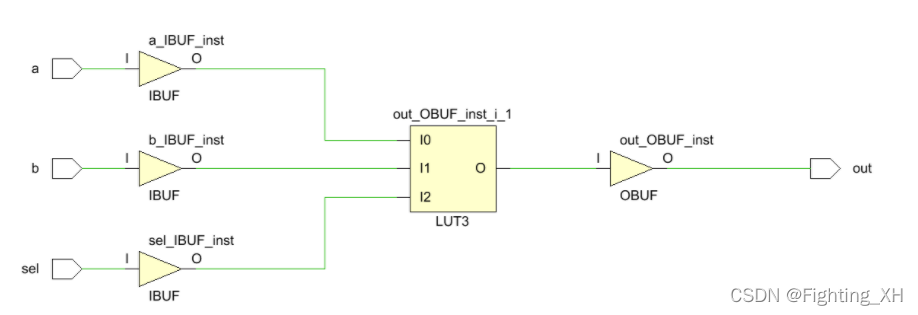

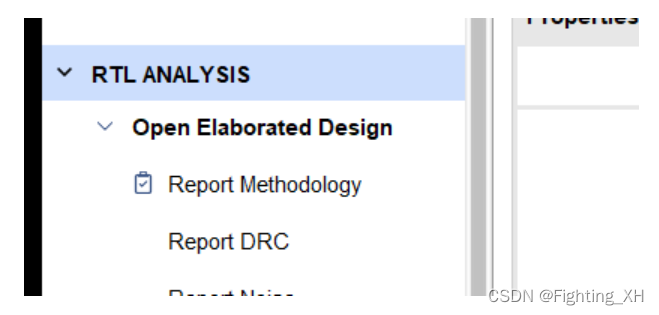

另外在如下橙色框处点击,还可查看RTL图

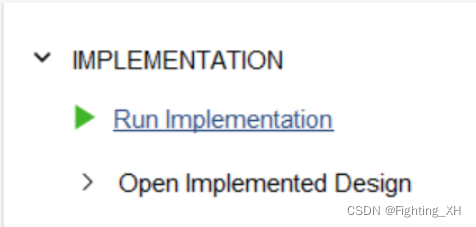

5、波形验证正确,进行布局布线

如何去看布局布线有没有完成:

-

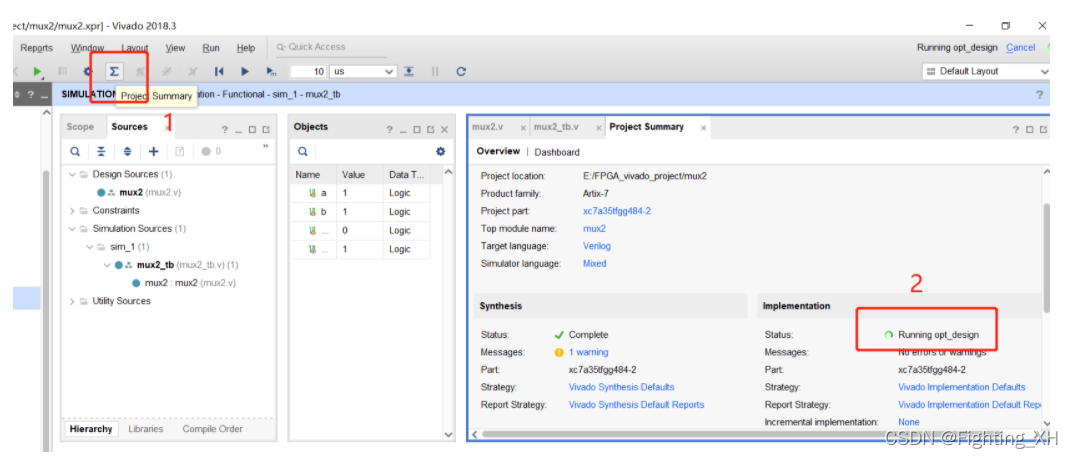

可以点击第一个红色框就会出现工程汇总

-

看第二个红色框,就能有绿色的圈,当出现对号的时候,说明布局布线完成

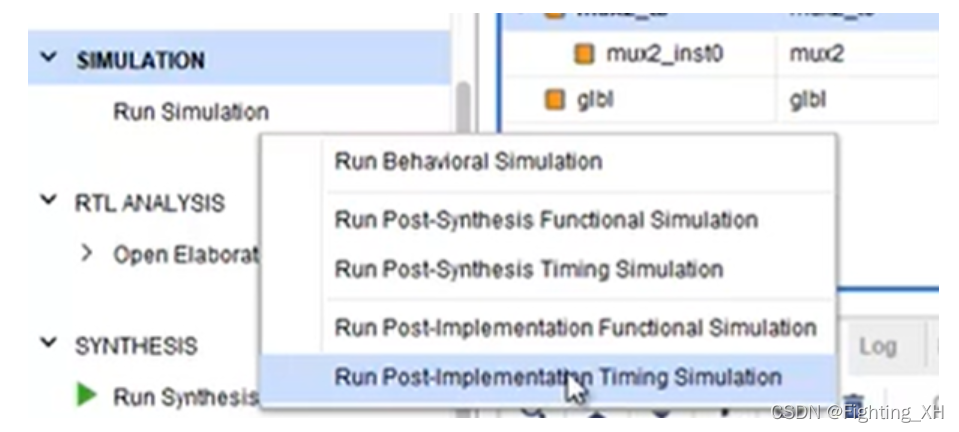

简单说一下,布局布线完成后开始时序仿真,我目前一般不需要这一步

-

功能仿真(前仿真)和时序仿真(后仿真)的区别在于:会有延迟的表现

-

本来b和out的上升沿应该完全对齐,但是现在没有对齐,而是延迟了5.592ns

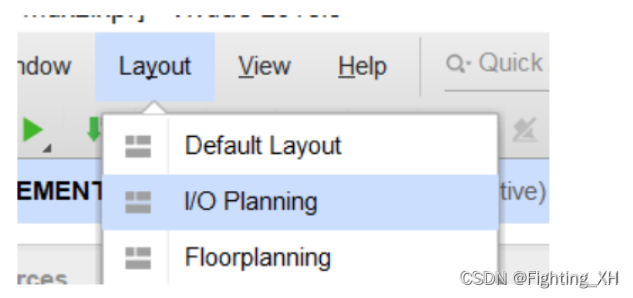

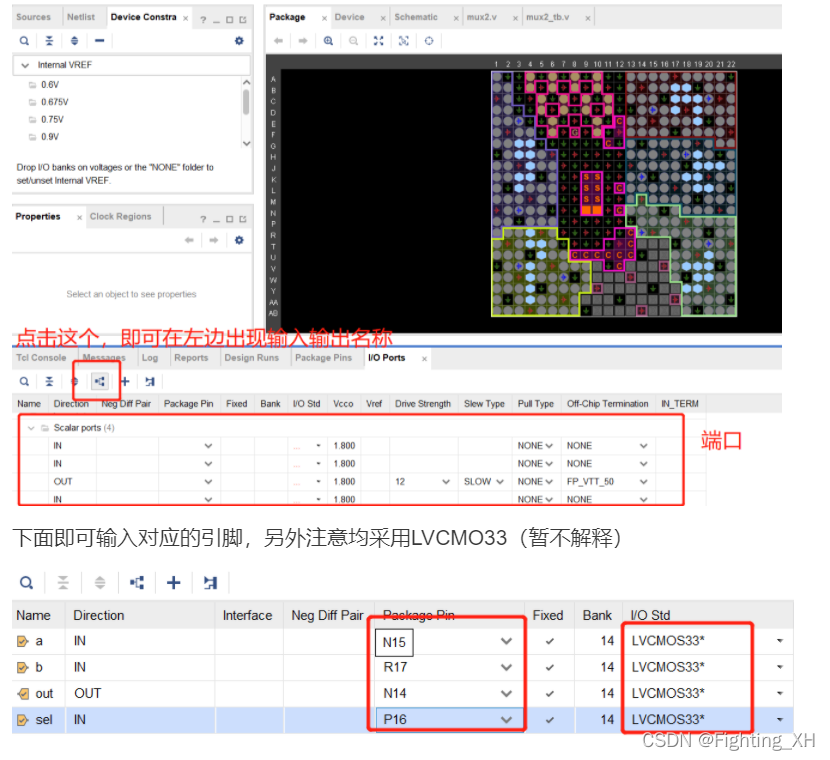

6、无错误后,进行引脚分配

先双击open

打开引脚分配

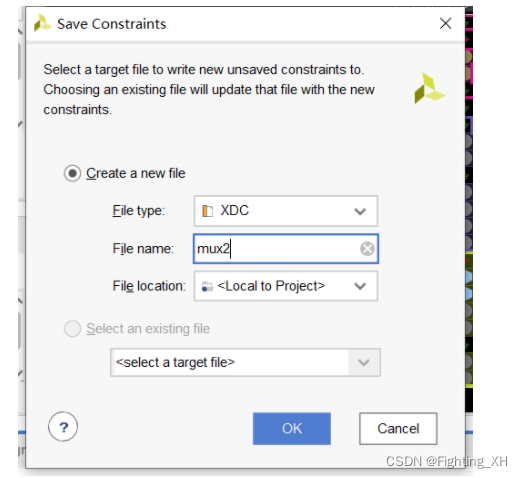

点击ctrl+s即可保存,和工程名字相同——ok

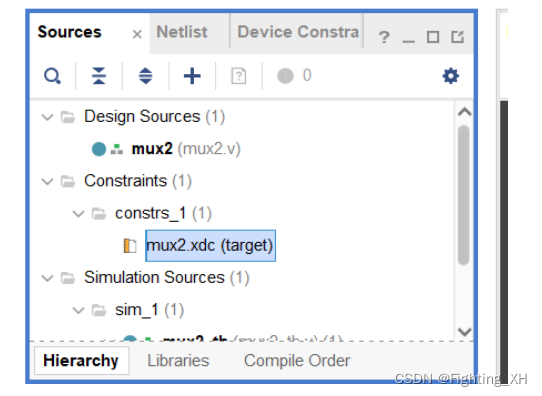

引脚分配完成后就能看到,资源里面,多了.xdc

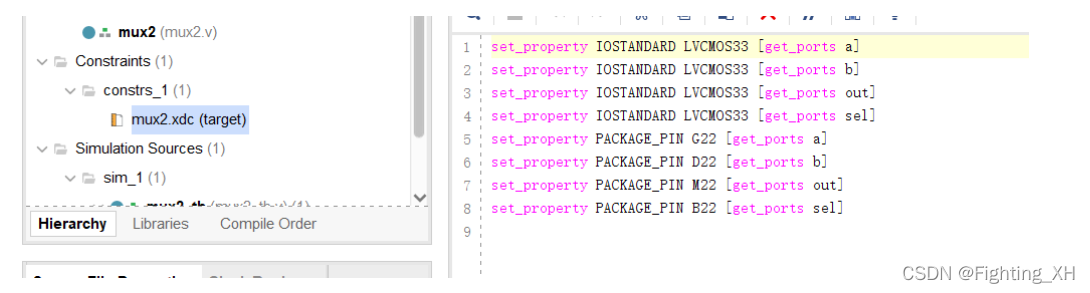

双击target文件:即可查看分配的引脚

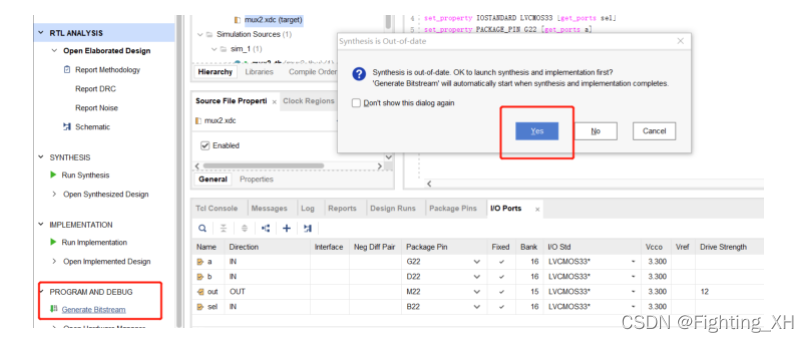

7、生成比特流文件

点击下面红色框,生成比特流,为了下载到开发板上去

在此双击生成比特流文件,然后即可点击项目汇总,等待生成成功。——如果引脚随意分配,很有可能是不能成功生成的。——分配的话是要符合基本架构的,比如一个开关,不能接到一个LED上面去

8、下载到开发板

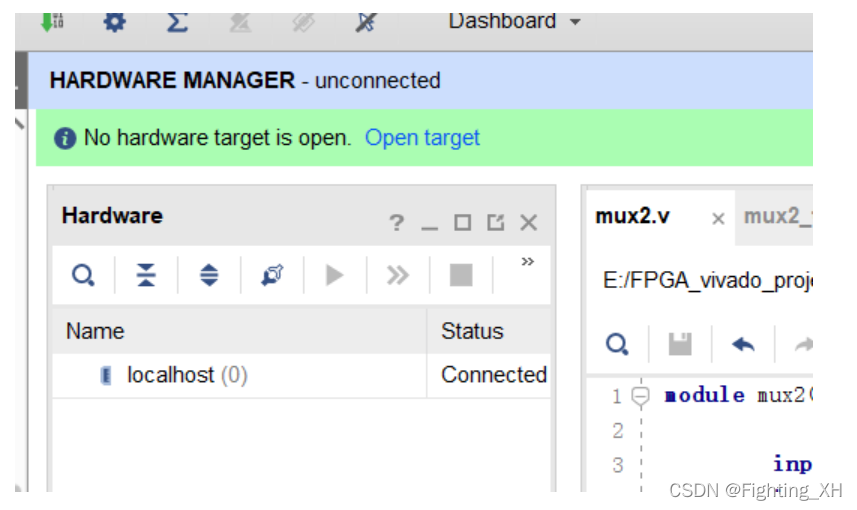

打开硬件管理器

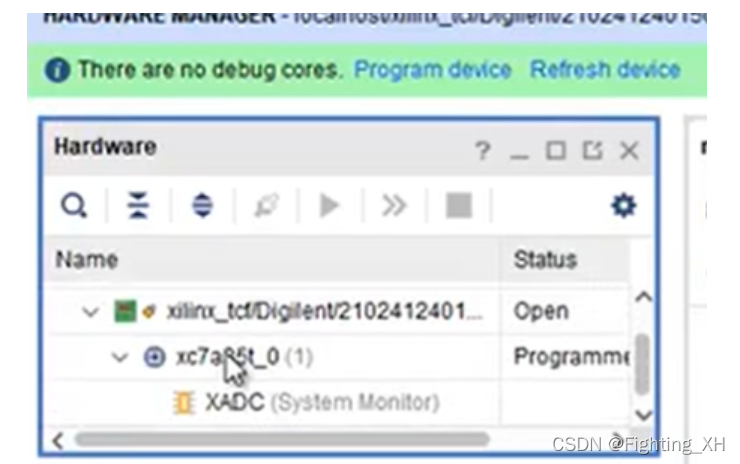

如果插上板子,还出现没有硬件,点击open target,然后自动连接

即可出现如下:右键——program即可

然后即可在开发板进行调试。

二、总结

PL部分的设计流程

- Vivado创建工程

- 添加V文件并编写代码

- 添加仿真文件,编写仿真代码

- 进行仿真验证

- 布局布线

- 引脚分配

- 生成比特流文件

- 下载到开发板

熟悉PL部分设计流程之后,然后就可以继续进行PS部分的学习啦!

参考:

1 小梅哥zynq SOC 的视频

2 (主要学习引脚约束文件咋写)

1099

1099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?