简介

SystemC是基于C++语言(最新版已支持C17特性)的扩展库,是为了解决跨越软件和硬件的一种系统级设计,高级综合,建模,验证的语言,可用于软件开发、软件性能分析、架构性能分析、硬件验证多种场景。SystemC最早源于非盈利组织🔗Open SystemC Initiative(OSCI),后来归属于🔗Accellera Systems Initiative(ASI) SystemC,并成为众多IEEE标准之一。

本篇侧重SystemC在Verification方面的介绍,ESL建模感兴趣的可查看:🔗ESL发展及其在项目中的应用,🔗漫谈芯片建模

ESL Modeling

ESL(Electronic System Level)建模不是某种具体的设计语言、工具或平台,而是一种通用的设计和验证方法学;就像验证中的UVM方法学可以通过SystemVerilog实现,而SystemC可以作为ESL的开发类库。(因为是一种方法学,UVM也可以通过SystemC,Python等语言实现,ESL除了SystemC,也存在LISA+语言)

根据时序精度,模型可分为三种:Cycle Acccurate(CA),Approximately Timed(AT),Lossely Timed(LT),对时序精度要求更高,则对建模抽象层次要求也更低,其仿真速度就越低,如下图:

ARM除提供RTL的IP外,其IP也有相应的🔗Cycle Model和Fast Model;Cycle Model的优势是cycle accuracy,直接从RTL代码编译出来,和RTL的时序100%匹配,可用于仿真验证,性能分析、体系结构决策和裸机固件开发。Fast Model的优势是high performance,软件可以基于虚拟原型(Virtual Prototyping VP),在硬件RTL没有ready的情况下,实现软硬件并行开发,也就是软件开发(侧重硬件功能而不关心时序)的左移(Shift-left)。

SystemC

可参考的学习资料:

🔗learnsystemc 中提供了SystemC语法的examples,参考🔗multi-language verification (一)DVT-Eclipse配置SystemC开发环境配置并运行这些examples:

SC_ROOT = /home/holden/systemc_work/lib/systemc-2.3.3

MAIN_CODE = -O0 -g -Wall -lsystemc -I${SYSTEMC_HOME}/include -L${SYSTEMC_HOME}/lib-linux64 -Wl,-rpath=${SYSTEMC_HOME}/lib-linux64

all: clean

#g++ -o exe ${MAIN_CODE} ./00_hello_world/hello_world.cpp

#g++ -o exe ${MAIN_CODE} ./01_module/module.cpp

#g++ -o exe ${MAIN_CODE} ./02_sc_ctor/sc_ctor.cpp

#g++ -o exe ${MAIN_CODE} ./03_sc_has_process/sc_has_process.cpp

#g++ -o exe ${MAIN_CODE} ./04_simu_process/simu_process.cpp

#g++ -o exe ${MAIN_CODE} ./05_simu_stage/simu_stage.cpp

#g++ -o exe ${MAIN_CODE} ./06_time/time.cpp

#g++ -o exe ${MAIN_CODE} ./07_concurrency/concurr.cpp

g++ -o exe ${MAIN_CODE} ./08_event/event.cpp

#g++ -o exe ${MAIN_CODE} ./09_event_combined/event_combined.cpp

#g++ -o exe ${MAIN_CODE} ./10_delta_cycle/delta_cycle.cpp

#g++ -o exe ${MAIN_CODE} ./11_sensitivity/sensitivity.cpp

#g++ -o exe ${MAIN_CODE} ./12_initialization/initialization.cpp

#g++ -o exe ${MAIN_CODE} ./13_method/method.cpp

#g++ -o exe ${MAIN_CODE} ./14_event_queue/event_queue.cpp

#g++ -o exe ${MAIN_CODE} ./15_event_queue_combined/event_queue_combined.cpp

#g++ -o exe ${MAIN_CODE} ./16_channel_mutex/mutex.cpp

#g++ -o exe ${MAIN_CODE} ./17_channel_semaphore/semaphore.cpp

#g++ -o exe ${MAIN_CODE} ./18_channel_fifo/fifo.cpp

#g++ -o exe ${MAIN_CODE} ./19_signal_readwrite/signal_readwrite.cpp

#g++ -o exe ${MAIN_CODE} ./20_signal_event/signal_event.cpp

#g++ -o exe ${MAIN_CODE} ./21_signal_many_writer/signal_many_writer.cpp

#g++ -o exe ${MAIN_CODE} ./22_resolved_signal/resolved_signal.cpp

#g++ -o exe ${MAIN_CODE} ./23_signal_bool/signal_bool.cpp

#g++ -o exe ${MAIN_CODE} ./24_buffer/buffer.cpp

#g++ -o exe ${MAIN_CODE} ./25_port/port.cpp

#g++ -o exe ${MAIN_CODE} ./26_export/export.cpp

#g++ -o exe ${MAIN_CODE} ./27_port2port/port2port.cpp

#g++ -o exe ${MAIN_CODE} ./28_specialized_port/specialized_port.cpp

#g++ -o exe ${MAIN_CODE} ./29_port_array/port_array.cpp

#g++ -o exe ${MAIN_CODE} ./30_primitive_channel/prim_channel.cpp

#g++ -o exe ${MAIN_CODE} ./31_hierarchical_channel/hierarchical_channel.cpp

#g++ -o exe ${MAIN_CODE} ./32_trace/trace.cpp

#g++ -o exe ${MAIN_CODE} ./33_report/report.cpp

#g++ -o exe ${MAIN_CODE} ./34_customized_datatype/customized_datatype.cpp

#g++ -o exe ${MAIN_CODE} ./35_clock/clock.cpp

#g++ -o exe ${MAIN_CODE} ./36_cthread/cthread.cpp

#g++ -o exe ${MAIN_CODE} ./00_trigger_when_busy/trigger.cpp

#g++ -o exe ${MAIN_CODE} ./01_trigger_when_busy2/trigger2.cpp

#g++ -o exe ${MAIN_CODE} ./02_interrupt_when_busy/interrupt.cpp

#g++ -o exe ${MAIN_CODE} ./03_interrupt_when_busy2/interrupt2.cpp

clean:

rm -rf *o exe

🔗中文书籍《SystemC 电子系统级设计》

🔗Cadence Support中关于SystemC的系列课程:

更多内容:🔗芯片仿真-资料汇总

SystemC for verification (Ⅰ)

基于SystemC,一些用于Verification和Validation的库如下:

OSCI组织提供的相关库:

🔗SystemC Verification Library (SCV) 2.0.1

SystemC Verification Library (SCV) 是一个用于 SystemC 验证的库。它提供了一组工具和类,用于简化验证环境的开发和管理。以下是关于 SCV 的一些重要信息:

- 版本和兼容性:

- SCV 2.0.1 是生产版本,支持 Accellera SystemC 版本 2.3.1、2.3.0(符合 IEEE Std 1666-2011)以及版本 2.2.0(符合 IEEE Std 1666-2005)。

- SCV 2.0.1 在多个平台上经过充分测试,包括 64 位 Linux、64 位 Linux(32 位编译器)、64 位 Mac OS X 和 32 位 Mac OS X。

- 功能和用途:

- SCV 提供了验证扩展,帮助验证工程师构建高效的验证环境。

- 它包含了一组类,用于处理随机性、约束、覆盖率、事务级别建模等验证任务。

- 示例和支持:

- SCV 附带了示例,帮助用户理解如何使用库中的功能。

- 支持最新的编译器版本。

(目前SCV仅处于维护状态,不再主动更新)

🔗UVM-SystemC Library 1.0-beta5

UVM-SystemC(UVM-SC)是参照UVM-SystemVerilog(UVM-SV)由SystemC/C++语言实现的一套用于验证的方法学库。ESL 设计可以借助UVM-SC 对完整 SoC 中运行的硬件和嵌入式软件模型进行验证。借助UVM的各类机制,如phasing, factory, configuration, reporting,register_model等,使得ESL验证也更加标准化。

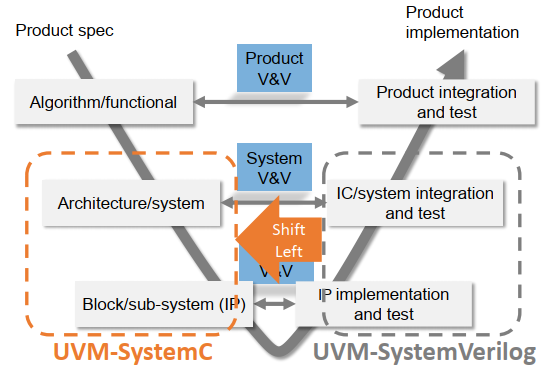

UVM-SV面向block-level,UVM-SC面向system-level;系统和软件工程师可以使用UVM-SC开发原型平台或者虚拟原型的验证环境,因为其统一的UVM结构,也方便后续IC验证团队复用;实现跨verification(rtl simulation)和 validatoin(HW-prototyping)的测试用例和测试平台的复用。

2011 年 9 月,作为第 7 个框架计划的一部分的欧洲项目成立,将 UVM 移植到 SystemC。 被称为异构可靠设计和集成验证(VERDI),主要目标是为异构系统开发统一的系统级验证方法。 VERDI 的合作伙伴包括Fraunhofer、NXP、Infineon、Continental、Magillem 和 UPMC。 经过三年的合作,VERDI 项目于 2014 年 10 月结束,为进一步标准化提供了语言参考手册 (LRM) 和参考实施。

🔗Accellera’s UVM in SystemC Standardization: Going Universal for ESL

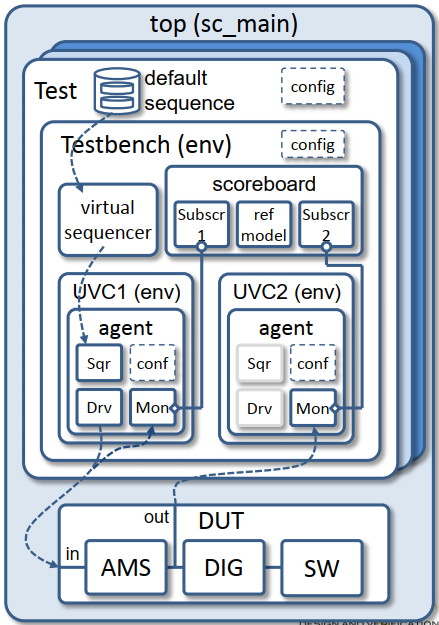

标准的UVM框图:

对于同一份产品规格书,从系统层面提前开展一些validation工作,实现系统级verification工作的左移; IP级的RTL和ESL模型也可以同步开发验证,并实现用例和平台复用。

UVM-Python:

🔗pyuvm:使用Python语言实现UVM框架,基于🔗cocotb开发。

🔗Constrained Randomization(CRAVE)

CRAVE:用于扩充UVM-SC的约束随机功能,CRAVE 库可以与 UVM-SystemC 结合使用。CRAVE 的语法被设计为自然适合 C++ 和 SystemC。CRAVE 库包括基于 BDD 和基于 SAT/SMT 的现代约束求解器。

🔗Functional Coverage(FC4SC)

FC4SC:实现覆盖率驱动的验证,可以使用功能覆盖率库FC4SC。FC4SC 提供覆盖组、箱和覆盖点的声明,以实现基于类型和实例的功能覆盖。FC4SC库将以统一覆盖互操作性标准(UCIS)格式存储覆盖结果,从而可以无缝地包含在市场上可用的各种EDA解决方案中。

SystemC Assertions(SCA)

使用SystemC构造assertion断言,正在开发中。UVM-SC还在逐步完善中,尚未加入IEEE标准。

SystemC for verification (Ⅱ)

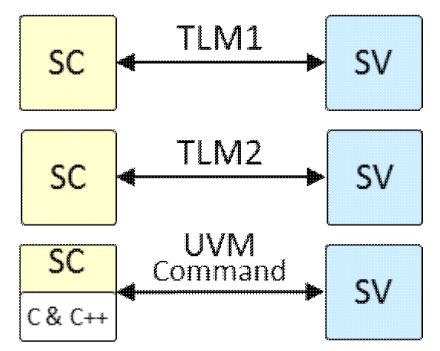

实际IC验证工作中,使用SystemC更多的是将其作为reference model的wrapper,利用TLM接口和UVM-SV通信。相比TLM1,TLM2库专门为建模存储器映射的片上总线而设计;

TLM2新增标准事务处理类generic_payload,利于不同的模型之间的互联互通性,每个generic payload有一组标准总线属性:command,address,data,byte enables,streaming width和response status;TLM1没有时间标注(Time Annotation),因此,不同模型之间缺乏标准的交换时间信息的方法 。TLM1中一般通过调用 wait 函数来实现延迟 ,仿真速度较慢 。 TLM2在阻塞和非阻塞传送接口中添加了时间标注,该方式的访真速度要快得多。TLM2支持松散定时(Loosely Timed ,LT)建模和近似定时建模(Approximately Timed)。

UVM-SV库中包含TLM2.0的systemverilog实现,但较少在验证环境中使用。因为TLM2主要是为了包含时序的建模用途,验证大部分场景使用TLM1足以。新版的SystemC库,已将TLM2.0库包含在内。

SC和SV混仿:

三大EDA对SC和SV混仿都有各自的仿真命令,库,相应配置的支持;

xrun和vcs都支持直接编译.c/.cpp文件,本质是封装了gcc/g++的调用命令。S家的syscan和vlogan可分别对SC和SV代码编译,vcs再对SC和SV的目标文件在elaboration阶段做link,生成可运行程序./simv;也可以直接使用g++将SC库和代码生成动态库.so文件,最后在运行仿真命令阶段,通过-sv_lib或者-sv_liblist加载动态库。

SC和SV混仿分为Pin level和Transaction level;

Pin level就是SC和SV两侧signal级别的连接,SC和SV可以相互例化另一种语言的模块;Pin level的仿真,需要各自EDA工具的支持,使用方式并不相同,无法直接做到在不同的仿真工具之间迁移;

Transaction level是基于TLM1.0/TLM2.0的通信,实现SV的TLM1.0/TLM2.0和SC的TLM1.0/TLM2.0相互通信,各家EDA均有不用的库来支持;库中包含SC/SV交互的底层基础实现,通过VPI/DPI实现跨语言的交互。这些库适配各家EDA工具。

S家的TLI:

TLI(Transaction Level Interface)是S家用于SC/SV TLM通信的库,TLM库未被开源,应该只可以在vcs上使用;路径:$VCS_HOME/etc/systemc/tlm/tli。

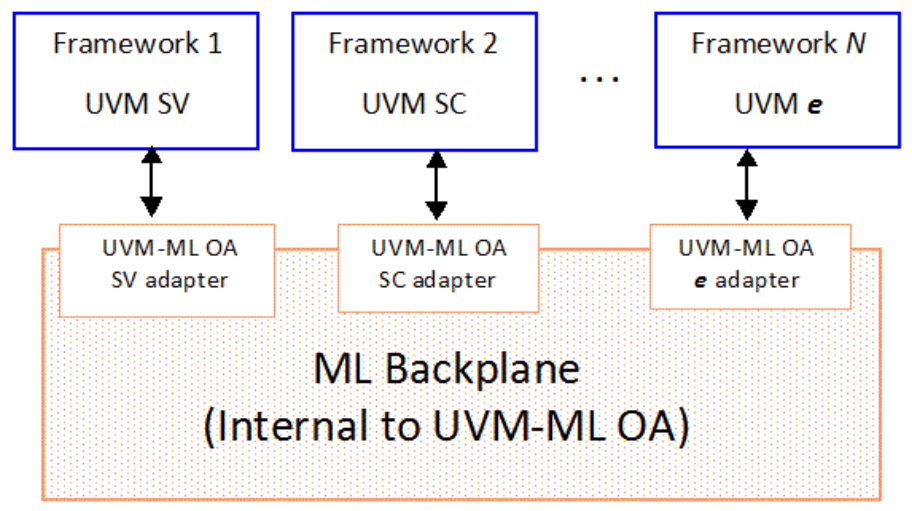

C家的UVM-ML OA:

UVM-ML OA(UVM Multi-Language Open Architecture package):是一种用于集成不同语言编写的验证组件的模块化解决方案。由Cadence和AMD共同开发的开源库,最新版🔗version 1.13已支持systemc2.3.3。UML-ML除了支持SV/SC语言外,还支持e语言(早期的一种和SV类似的面向对象的验证语言,现已被弃用)。

UVM-ML库中的Backplan库为CPP/SV/e语言提供各种库函数,利用各语言的adapter,实现不同语言的通信。

本系列🔗multi-language verification (五)UVM-SV通过DPI或者SC-UVM_ML库调用Matlab一篇中提供了一个利用UVM-ML OA库封装调用matlab程序的示例。

M家的UVMC:

UVMC(UVM Connect):是M家开发的用于SC/SV TLM通信的库,最新版为🔗UVMC-2.3.3;相比于UVM-ML库,UVMC更加轻量化,关注于TLM的connect。而UVM-ML还额外支持e语言,支持验证组件的结构适配等其他功能。

本系列🔗multi-language verification (六)UVM-SV通过DPI或者SC-UVMC库调用Python一篇中提供了一个利用UVMC库封装调用Python程序的示例。

上述三各库,底层都是利用DPI封装API,然后将一种语言域中的transaction的数据结构pack打包为比特流,传递到另一种语言域;另一种语言域通过unpack操作将比特流解压到本语言域的transaction中;所以要求两个语言域的transaction数据结构一一对应,这样才可以正确处理;各库都提供了相应的utiles,方便根据数据结构自动生成相应的pack/unpack函数。

上述介绍的详细内容可参考各仿真工具的userguide,库的相关文档,examples示例。

The future of Multi-Language

accellera组织已经成立了🔗Multi-Language (ML) 工作小组,致力于Multi Language Verification(MLV)的标准化工作;未来,UVM-SC和UVM-SV两个语言域相互打通,两侧的phase同步,resource database共享,event握手等UVM特性将实现互通。🔗DVCon US 2021 “Short Workshop”

除了SC和SV两大语言,Matlab和Python也考虑加入Multi-Language标准化的范畴。

898

898

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?