1 概述

在FPGA开发中很多商用IP核出于知识产权保护的目的,不提供源代码,而是提供综合后的FPGA网表。由于没有源代码,也无法对网表文件直接进行仿真的操作来验证功能,此时需要独立的仿真模型文件。

本文介绍在Xilinx(AMD) vivado软件下对FPGA代码综合生成网表、网表的仿真模型,以及使用仿真模型对网表进行仿真的方法。

2 FPGA网表

在vivado软件下有edf和dcp两种格式的网表文件。

2.1 综合设置

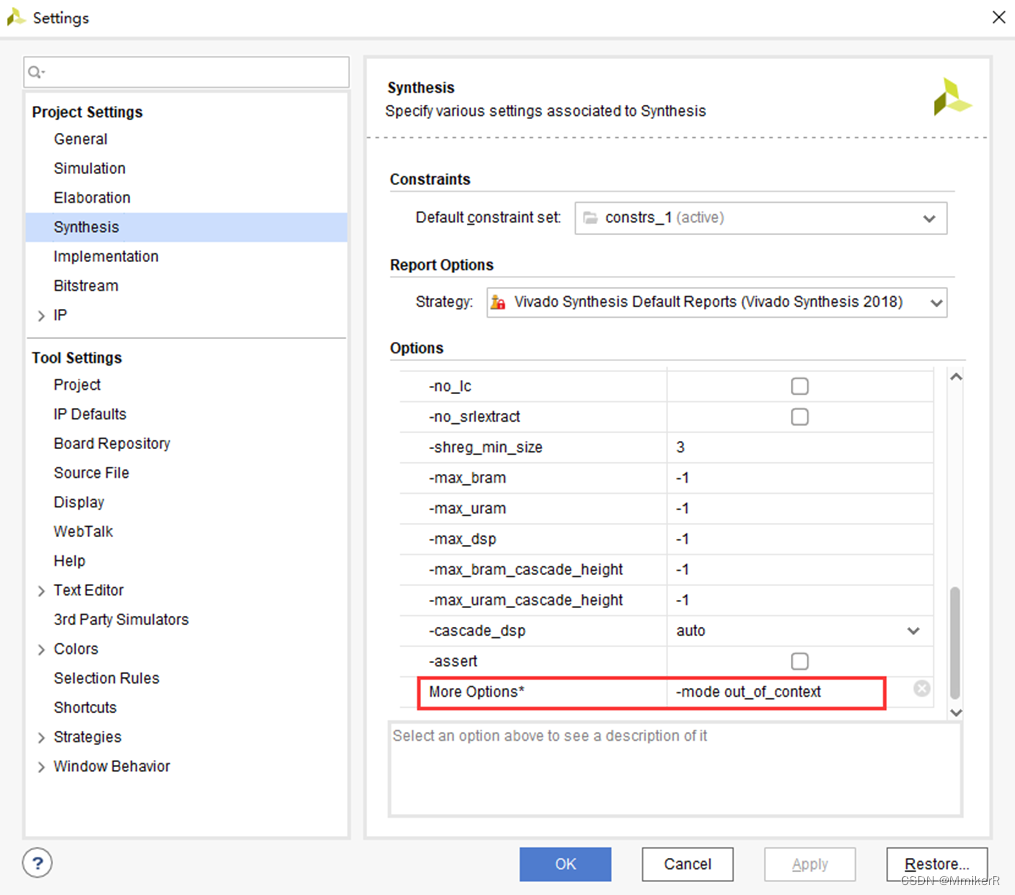

网表生成前的综合设置,需要添加-mode out_of_context选项。在综合时vivado软件将不给顶层模块的input和output插入IO buffer。

其余选项可以根据具体需求来选择。通常也有人会将代码的模块层次去除,在综合后的网表里就看不到模块的层次结构。

设置完成后点击综合即可。

2.2 生成网表文件

综合完成后,dcp格式的网表文件可以直接在工程目录下.runs\synth_1路径下找到与顶层模块同名的.dcp后缀的文件。

生成edf格式的网表则需要进行额外几步操作。

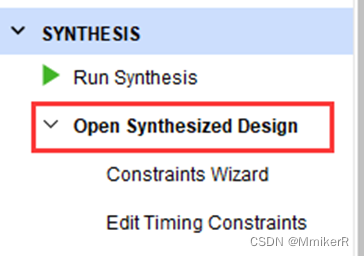

1、打开综合结果

2、指定edf存放路径

在Tcl Console输入例如:

cd E:/XXX/YYY/ZZZ/3、生成edf网表端口描述文件

在Tcl Console输入:

vivado 2017.4及以前

write_verilog -mode port <design_name>.vvivado 2018.1及以后

write_verilog -mode synth_stub <design_name>.v4、生成edf网表文件

在Tcl Console输入:

模块不包含Xilinx的IP

write_edif <design_name>.edf模块包含Xilinx的IP

write_edif -security_mode all <design_name>.edf2.3 生成仿真模型

1、指定文件存放路径

在Tcl Console输入例如:

cd E:/XXX/YYY/ZZZ/2、生成仿真模型

在Tcl Console输入:

write_verilog -force -mode funcsim <design_name>_sim_model.v3 仿真模型使用

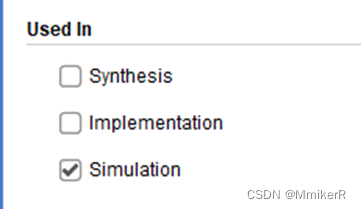

将生成的仿真模型<design_name>_sim_model.v添加到工程仿真文件中,为了防止与源文件冲突,设置其仅用于仿真。

仿真模型可以用于综合前的行为仿真和综合后的功能仿真。

可以直接使用仿真源文件的test bench对仿真模型进行仿真,无需做修改。仿真模型的仿真速度会比源文件的仿真速度慢很多。

8575

8575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?