参考:《高速电路设计实践》

目录

1、TTL和CMOS电平不适于高速应用的原因

TTL和CMOS电平是电路设计中十分常见的电平选型,但不适于高速应用。主要原因如下:

(1)电平幅度大。导致信号变化沿所耗费的时间较长,不适于传输频率达到200MHz以上的信号。

(2)输出信号为单端,在传输路径上易受到干扰,不利于远距离的传输。

(3)功耗较大。TTL器件静态功耗较大,即使是静态功耗较小的CMOS器件,由于电平摆幅宽,其动态功耗也偏大。

2、高速电平的优势

在高速设计中,需要选择电平摆幅窄、支持远距离传输、功耗小的信号电平。LVDS、LVPECL、CML等电平具有这些特性。

高速电平一般都采用了差分技术,它具有很多优势:

(1)抗干扰能力强。

由于构成差分的两个导线距离很近,产生的干扰很接近,做差之后的逻辑判断上的干扰会被抵消。

(2)对参考平面(地平面或电源平面)完整性要求较弱。

差分对内两信号是寻找阻抗最小的路径以实现回流,该路径一般选取为临近的地或电源参考平面。与差分对内两信号的驱动路径相同,回流路径上的信号也具有大小相等、方向相反的特性,从而相互抵消,最终的结果是几乎没有任何电流从参考平面流过。所以即使参考平面不完整,差分对信号所受的影响也比较小。

(3)抑制串扰、EMI能力强。

单端信号线之间不能相距太近,否则会出现串扰、EMI等问题。而对差分信号而言,由于两条相邻的导线所承载的电流大小相等、方向相反,所以对内两条导线之间,相距越近、周围信号线和信号过孔分配越均衡,则产生的磁场越接近完全抵消的状态。

(4)功耗小、速率高、不受温度、电压波动的影响。

由于差分信号逻辑状态变化的参考点位于差分对内两信号边沿的交叉点,且幅值用两信号的差值表示,无需和GND比较,因此信号摆幅小、速率高。同时温度、电压的影响会由于差分对内两信号相距相近,干扰一致,相互抵消。

3、案例:差分对走线附近信号分布不均衡造成电磁辐射

某产品在进行EMC(电磁兼容性)测试时,发现在用户面板上USB口附近,399MHz辐射超标。

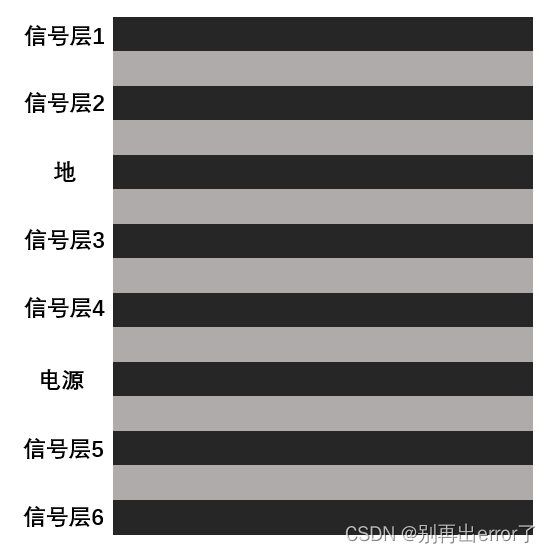

单板为八层板,层叠结构如图:

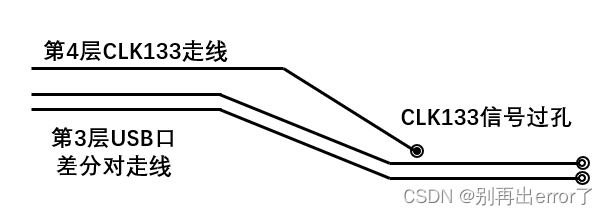

USB口差分对信号在信号层3传输。差分对信号走线等长、对内两信号间距相等,且阻抗匹配。而由于信号层4时邻近层,两层结构如图:

在第4层有一个频率为133MHz的时钟信号CLK133,距离3层的差分对信号仅有2mil,且与差分信号平行走线的长度长达1400mil。同时在距离差分信号线7mil的位置有一个CLK133的过孔。

辐射超标的399MHz是133MHz的三次谐波,将时钟驱动器关闭测试EMC发现不存在辐射超标现象。

改进:将CLK133信号线及其过孔距离增大为20mil,问题解决。

拓展:

(1)差分对内两信号走线长度相等,以满足时序要求和共模噪声。(差分对信号的时序参考点是对内两信号边沿的交叉点;长度不等时引起的共模噪声会带来严重的EMI问题)

(2)差分对内两信号的间距越小越好。越接近,附近的干扰越接近抵消;差分对内两信号的电流方向相反,形成了电流回路,会形成磁场,越接近越能减小电磁干扰。

(3)差分对内两信号的间距保持一定。

(4)差分对信号的阻抗控制。取决于:信号线宽度、铜箔厚度、两信号间距、差分对信号距离参考平面的距离、

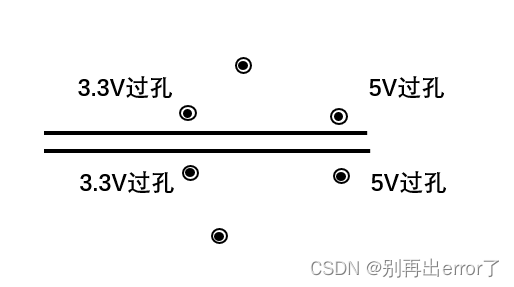

(5)尽量保证差分对信号线附近过孔的均衡分布。过孔均衡分布有利于抵消干扰。如图:

DONE!

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?