说在开头:关于光的波粒之争(2)

1793年,19岁的托马斯.杨受到他叔父(医生)的影响,决定去伦敦学习医学,他研究了人体眼睛的构造,开始接触光学上的一些基本问题,并最终形成了光是波动的想法。普通物质是有累加性的:一滴水加一滴水就是两滴水,不会消失的;但是波动就不同了,如下图所示两列普通的波相遇,如果他们正好波峰对波峰,那么叠加起来是两倍高,但是如果是波峰对着波谷,那么他们将相互抵消。他在研究牛顿环的明暗条纹时,被这个关于波动的想法给深深打动了。

1801年和1803年托马斯.杨分别发表论文,阐述了如何用光波的干涉效应来解释牛顿环和衍射效应,甚至通过实验数据计算出了光波长在1/60000~1/36000英寸之间;1807年总结出版了他的《自然哲学讲义》,里面综合整理了他在光学方面工作,并第一次描述了他那个扬名四海的实验:光的双缝干涉(一直到现在还有人在做,一做就是好几百年~)。物理史上“第二次波粒战争”开始了,干涉条纹这门波动大炮的杀伤力终于惊动了整个微粒军团,无论微粒怎么努力都解释不了:为什么两道光叠加在一起反而造成黑暗?而波动的理由却简单而直接:屏幕上某点的距离有所不同,当这个距离是波长整数倍时,两列光波正好互相加强形成亮带;反之距离刚好半个波长相位差时,两列波正好相互抵消而变成暗带。

决定性的时刻来到了1819年,而在1818年法国科学院发起一个悬赏征文:利用精密的实验确定光的衍射效应以及推导光线通过物体附近时的运动情况。评委有许多知名科学家组成,其中:比奥、拉普拉斯和泊松都是微粒说的拥护者。但戏剧性的一幕出现了:一个不知名的法国年轻工程师——菲涅尔向评委会提交了一篇论文,他采用了波动的观点,并以严密的数学推理,极为圆满地解释了光的衍射问题。泊松并不相信这一结论,对它进行了仔细的审查,结果发现当把这个理论应用于圆盘衍射时,在阴影中间将会出现一个亮斑。这不搞笑嘛?在泊松看来这相当荒唐,同时也差点让菲涅尔的论文中途夭折,幸亏菲涅尔的同事:评委之一的阿拉果,在关键时刻要坚持实验检测,结果发现还真的有一个亮点如同奇迹一般出现在圆盘阴影的正中心:位置和亮度和理论符合的相当完美(所以泊松亮斑,实际上应该称为:菲涅尔亮斑)。

菲涅尔不就后又作出了一个石破天惊的决定:他革命性的假设光是一种横波(类似于水波),而不像胡克以来大家一直认为的纵波(类似弹簧波,前后压缩传播),1821年,他发表了《关于偏振光线的相互作用》,用横波理论成功的解释了偏振现象。但是菲涅尔的横波理论却留给波动一个大难题:以太。光是一种横波,而且传播速度经测量达到30万公里/秒,在传统的波动论里,它的传播媒介必定是一种异常坚固的固体,甚至比最硬的金刚石还要硬不知多少倍。然而没有人能看到或摸到这种以太,而实验也无法测定它的存在,而且这些坚硬无比的以太却不能阻挡任何物体,哪怕是一粒灰尘的运动。

一代宗师麦克斯韦于1856年,1861年和1865年发表了三篇关于电磁理论的论文,这是一个开天辟地的工作,他在牛顿力学大厦之上又完整的建立了另一座大厦。麦克斯韦在1861年的第二篇论文《论物理线》中预言:光其实是电磁波的一种。(参考自:曹天元-上帝掷骰子吗)

三,电源分配网络的组成

通过上面两章节的介绍,我们理解了电源分配网络系统的基本概念,以及设计电源分配网络系统的总目标:单板电源分配网络阻抗要小于目标阻抗。但具体要怎么去做呢?首先需要了解电源分配网络具体有哪些部分组成。

前面分析电源分配网络阻抗产生的主要原因是:电感。任何器件、接口都存在寄生电感,取决于封装、过孔、以及过孔到电源/地平面连接处的扩散电感;所以电源分配网络的互连一般表现为:感性,同时意味着:高频时电源分配网络表现为一个高阻抗路径。

板级电源分配网络设计的频率范围一般约从100KHz到100MHz(根据器件具体要求),主要由PCB平面电容和MLCC电容器发挥作用。这是什么原因呢?单板上处理器以及高速器件的工作/接口频率远大于100MHz,超过100MHz的噪声难道就不需要关心了么?

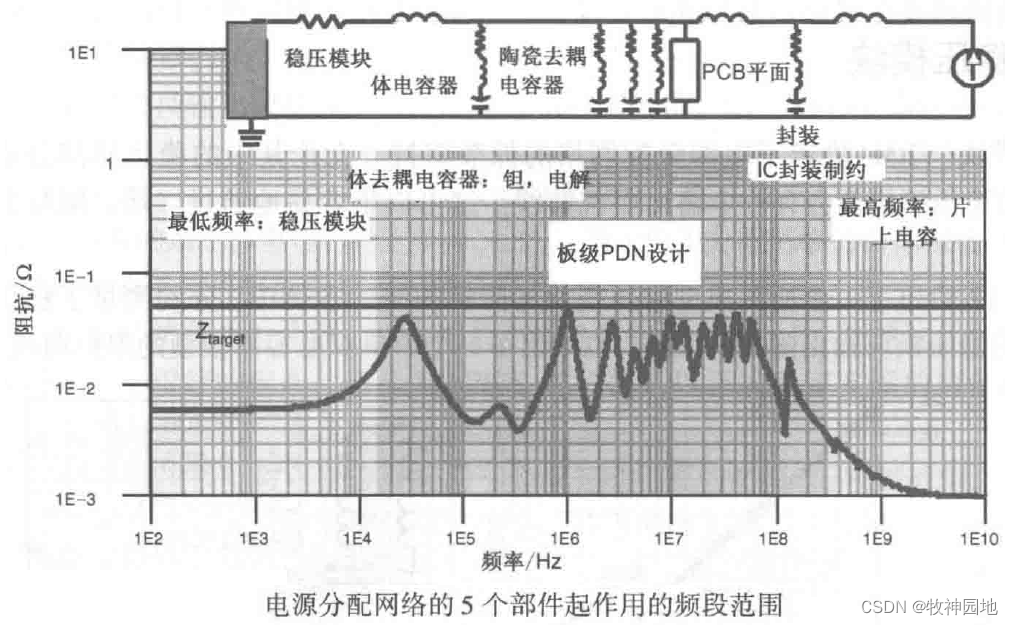

从某种角度来说,我们的确不需要关心超过100MHz的噪声。如下图为完整的电源分配网络拓扑图,不同频点对应不同的滤波器件。我们一起看下根据频段划分的电源分配网络组成:

1. 最低频段(0~10KHz):电源模块(VRM)决定了从器件看向电源分配网络的阻抗,电源模块性能起决定作用;

——低频段的电源分配网络阻抗相对较小(电感较小),通过调节电源模块的输出能力,提供了足够大的能量。

2. 在10~100KHz频段:滤波电容(大容量电解电容/钽电容)对电源分配网络阻抗起决定作用;

——此时靠电源模块的响应已来不及啦,需要滤波电容来提供瞬时大电流。

3. 在100KHz~100MHz频段:阻抗取决于去耦/旁路电容(nf级陶瓷电容)和PCB平面电容等;

——单板电源分配网络路径上的电感随频率增加,导致远端阻抗大增,只有器件附近的去耦/旁路电容才能起到滤波作用。

4. 器件封装内的电源分配网络的等效串联电感:制约着芯片(Die)向板级电源分配网络看过去的最高频率,这是板级电源分配网络设计的一个最高频率限制;

——器件管脚的串联寄生电感大小决定了板级滤波的作用频率;举个栗子,目标阻抗要求为0.5Ω,器件管脚寄生电感为1nH,可计算得到在100MHz频率下的阻抗约为0.6Ω,那么无论板级的电源分配网络阻抗多小(就算是0Ω),从器件内部向板级电源看去,其阻抗为0.6Ω> 目标阻抗0.5Ω;所以100MHz以上频率的电源分配网络阻抗,板级已起不到任何作用。

5. 所以当超过100MHz频率时:从器件看过去的电源分配网络阻抗只与封装和器件有关(片上电容和封装去耦电容);

——这就是为什么单板上去耦电容没必要对应芯片工作频率(GHz)来进行滤波设计的原因。

看到这里,可能有同学突然脑壳卡牢了,说:为啥大电容器滤低频段频率噪声,而小电容滤高频段噪声呢?根据Zc = 1/jωC来说,C越大那么容抗就越小;好,那么这位同学需要回去看一看《电容器原理》专题的相关章节了,看一看不同容值电容器的不同阻抗曲线是怎么样的。

那对于不同频率分量噪声呢,举个栗子,假如10KHz的噪声需要100uF电容器来滤除,那么100MHz的噪声用10nF级别的电容器来滤除;很明显100uF的电容器可以吸收的能量比10nF要大的多,那10nF够用么?

好,我们电容器滤波是其阻抗大小的问题,而非能量的问题。但我们也以从能量的角度来理解一下:对于相同幅值的一个波长的能量来说,低频率的信号噪声能量要大于高频率的;低频率噪声对电容器充电/放电时间要更长,所以电容器容量要更大以吸收更多的噪声能量,相反高频噪声对应的电容器在一个波长周期内吸收/释放的能量更小。

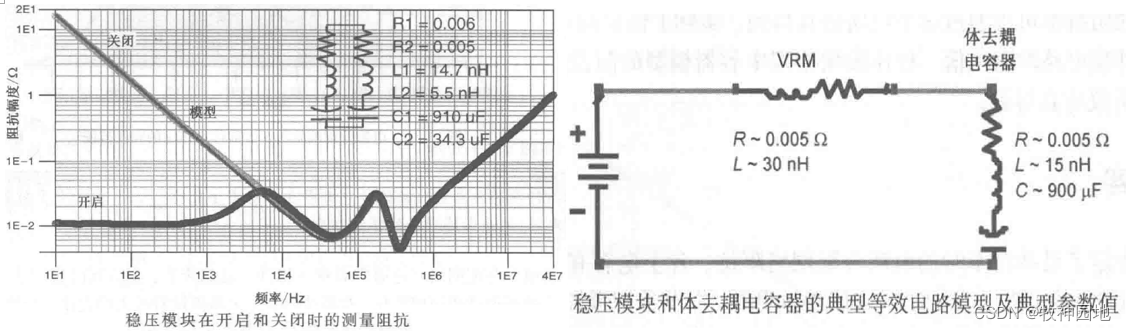

1,电源模块(VRM)

电源模块决定了电源分配网络的低频阻抗,所有的电源模块都会有一个输出阻抗曲线,如左下图所示,电源模块起作用的频段在0~4KHz左右;在4KHz以后的电源分配网络阻抗曲线与双电容模型一致。我们将电源分配网络按频率区域划分成3部分:

1. 在 < 1KHz时:若电源模块开启,输出阻抗会下降几个数量级,输出电压保持恒定,与其电流负载无关;

2. 在1KHz到4KHz时:阻抗不断增加, 4KHz时阻抗与电容其的阻抗相匹配;

3. 在 > 4KHz时:电源分配网络阻抗完全由无源电容所决定,电源模块不起作用。

所以所需滤波电容(电解电容)的总容量,可以通过电压模块不能维持低阻抗频率处(1KHz)的目标阻抗去估算:Cbulk > 1/(Ztarget*2π*1KHz) = 160uF/Ztarget。

在实际应用中,开关电源的输出阻抗模型很难获得,我们假设开关电源设计合理稳定(通过电源动态响应、环路稳定性、纹波电压等测试),保证在低频段区域满足电源响应的要求。

- 去耦电容

在<100KHz低频段时有电源模块(VRM)、滤波电容为单板电源分配网络提供低阻抗;但在> 100KHz频段就需要板载去耦电容(陶瓷去耦电容和电源/地平面电容)为电源分配网络提供低阻抗。

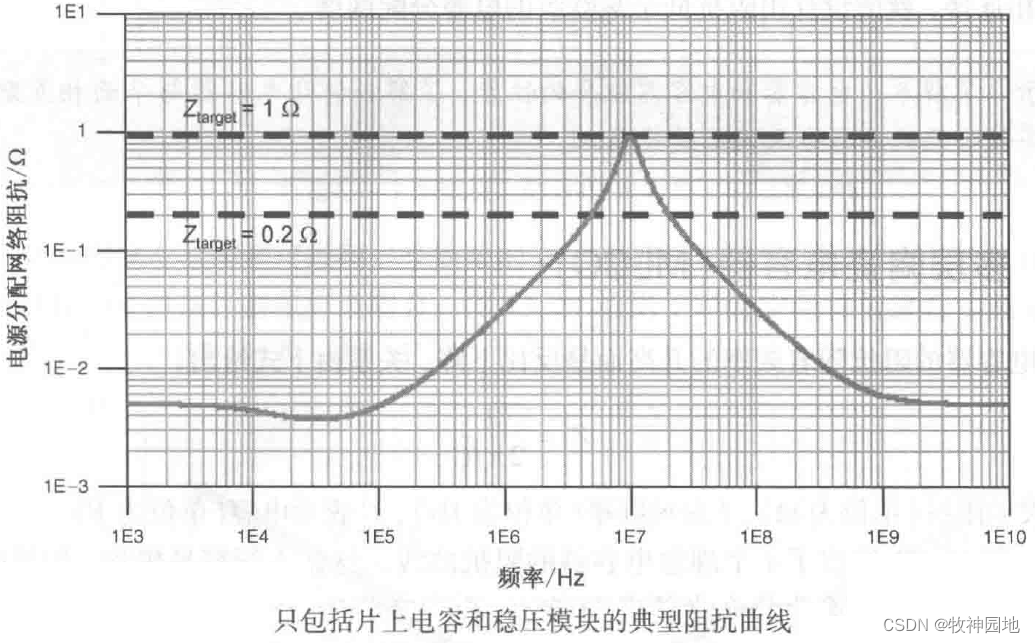

如下图为未加其它去耦电容器,只包括电源模块、滤波电容和50nF片上电容的电源分配网络阻抗;如果目标阻抗是1ohm,那么即使未加其它去耦电容器,也能满足电源分配网络设计要求,即使目标阻抗为0.2ohm,只要电流频谱幅度峰值在5~20MHz频率范围内没有出现尖峰,单板也能正常工作;此时无论板级电源分配网络如何设计,单板都能正常工作;会让人产生一种错觉:去耦电容并不那么重要!这是对去耦电容很大的误解,并不是所有的单板能够这么幸运。

2.1 去耦电容模型

理想电容器的阻抗随频率升高呈反比下降:Z=1/2πƒC,但是实际电容还有寄生电感和电阻,其行为不像理想电容;如下图所示,我们在《电容器》专题已经分析了:在有寄生电感和电阻的模型中,电阻、电感和电容都是理想元件,它们的参数随频率恒定不变(<1GHz),其阻抗曲线非常接近实际电容器的实测阻抗,在不同的频段呈现出不同的特性:

1. 低频时:自谐振频率以下,RLC电路阻抗取决于理想电容,电容呈现的是容性;

2. 高频时:自谐振频率以上,RLC电路阻抗取决于理想电感,电容呈现的是感性;

3. 自谐振频率点:理想电阻(ESR)决定了RLC的最低阻抗,电容呈现的是阻性。

自谐振频率点计算:ƒSRF = 1/2π*1/LC![]() = 159MHz/LC

= 159MHz/LC![]() 。

。

2.1 去耦电容的寄生电感(ESL)

寄生电感对电源分配网络非常重要,也是设计电源分配网络的原因(如果没有寄生电感,那么久不需要设计这么复杂的电源分配网络);电容器的寄生电感通常称为等效串联电感(ESL),ESL的值主要由电容器的安装方式决定:反映了安装方式的情况而不是电容本身。

——举个栗子,如下图所示,X2Y的电容并不是电容本身ESL较低,而是由于其特别的设计使得安装电感更小;这种安装方式:减小了ESL,使得自谐振频率点抬升,而在高频段由于ESL的减小,使得电容表现出更小的阻抗,这种安装方式减小ESL的同时也会影响ESR。

- 平面电容

根据电容的定义,任何两块导体中间夹着一块绝缘体都构成了电容;而电源与地平面之间明显也存在这个电容;同时电源-地平面电容的引脚电感(ESL)为0、ESR为0,所以在非常高频率上可以减少电源和地的噪声。

——根据传输线理论中的平面电容计算方法,平面电容容值为: C = 0.225*εr*A/d;假设电源-地距离为10mil,介质为FR-4材料,那么平面电容大小约为:100pf/in²。

如下图所示,平面电容是板级电源分配网络所能起到作用的最高频段,在PCB设计中要充分利用电源-地平面电容,尽量减小间距以增大平面电容容值,对电源分配网络阻抗设计至关重要。

- 封装屏蔽

集成电路封装是指:芯片(Die)焊盘与单板器件焊盘之间部分,包括:焊盘、键合线等;在电源/地的芯片焊盘到单板焊盘之间串联了一个封装引脚回路电感,成为电源分配网络阻抗的一道屏障:ZL = 2πƒL;跨过这道屏蔽,我们就进入了芯片(Die)内部了。

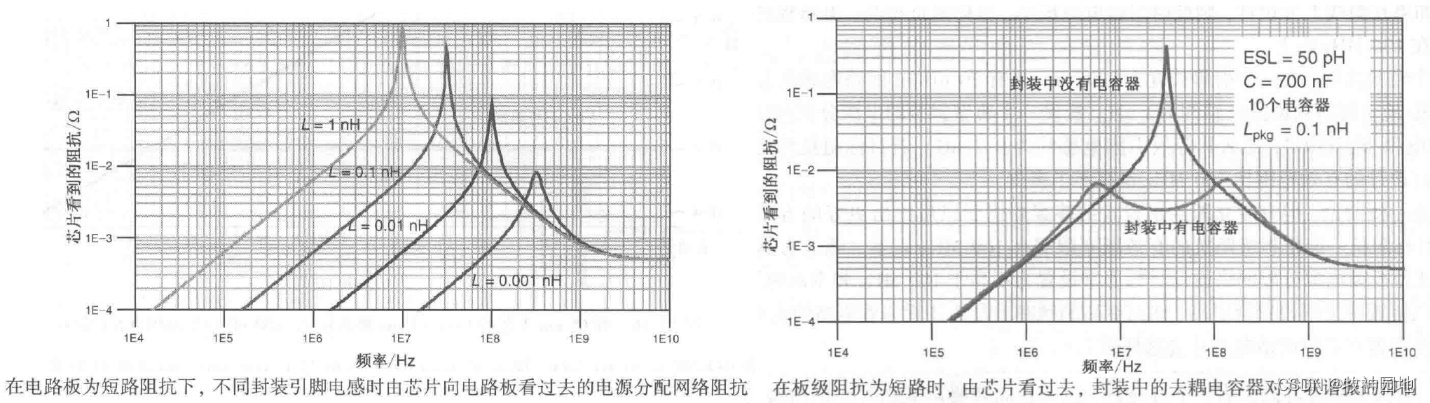

不同封装的引脚电感相差很大:大到几十nH小至几十pH;除了封装引脚电感,还有连到单板的过孔回路电感,以及电源/地平面上运送电流过程中的扩散电感。

考虑封装电感和片上电容的相互作用,单板为短路阻抗时由芯片看向电源分配网络阻抗曲线,如下左图所示,该阻抗由封装电感决定:无论怎么设计板级电源分配网络,都不可能将芯片(die)看向电源的网络分配阻抗减小到比封装引脚阻抗更小;由于封装电感与片上电容相互作用,会出现很大并联谐振阻抗尖峰,如下右图所示,此时可以通过封装中的去耦电容抑制。

——我早期接触到的有些CPU或DSP,很明显看到在器件表面焊接/排列了多个0201封装电容,这些电容就是用于器件封装和Die之间的滤波,抑制管脚电感的并联谐振阻抗尖峰。

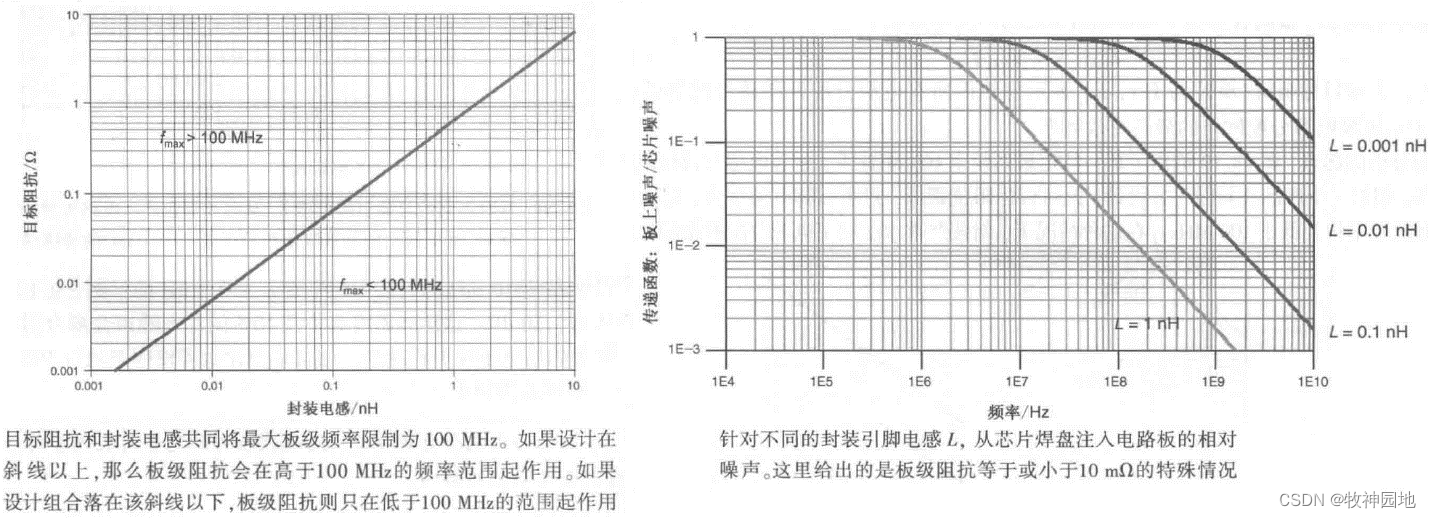

为了确定板级电源分配网络的设计目标,先确定由封装引脚、过孔和扩散电感共同组成的阻抗开始超过目标阻抗时的频点,这是板级阻抗对芯片发挥作用的高频上限频率;封装引脚电感、最高有效频率和目标阻抗之间的关系:Ztarget < 2π*Lpkg* ƒmax。

给出100MHz频率下,封装电感和目标阻抗的关系如左下图:如果单板目标阻抗在斜线下方,此时目标阻抗很低,封装引脚电感很大,那么单板最高有效频率低于100MHz;当封装中有去耦电容时,板级阻抗最高有效频率往往小于100MHz。

如右下图所示,封装电感大的另外一个好处是:它作为一个过滤器,以防止高频噪声从芯片的电源分配网络跑到单板上,封装引脚电感越高,板上电压噪声就越少。

- 片上电容

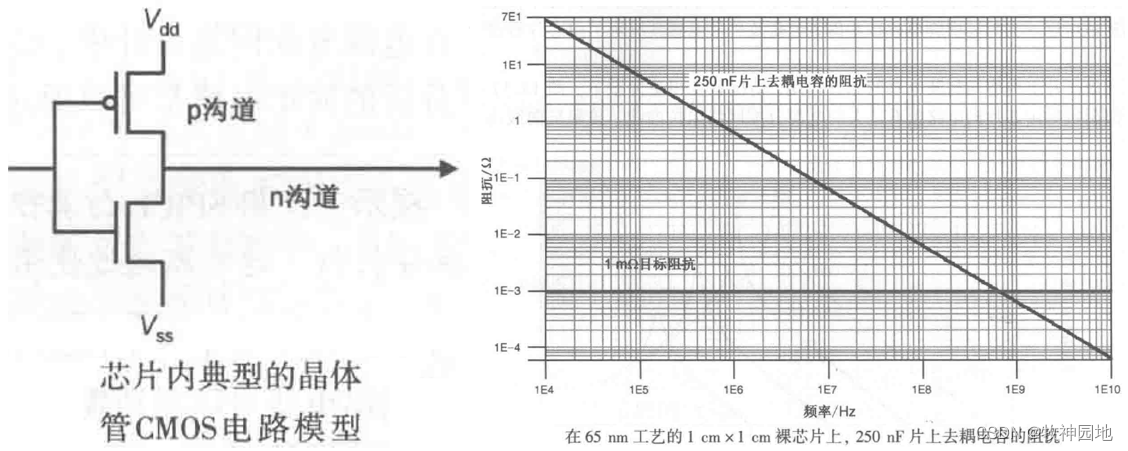

器件内部的滤波电容包括了:封装电容和片上电容;器件电容的作用已在上一节简单描述,而片上电容:决定了更高频段的电源分配网络阻抗。然而片上电容并不像封装电容,是一个个电容元器件,而是芯片内部的各种寄生电容:

1. 芯片内部电源层和地层之间的电容;

2. 所有P管/N管的栅极电容(栅极电容的具体分析,后续在《MOS管基础》专题详细讲解);

3. 其它各种寄生电容。

芯片上最大的电容源自分布在片上各处的栅极电容(面积大,数以百万计),在任何时刻PMOS和NMOS都是一个开启一个关闭;这意味着总有一个MOS管的栅极被连接到芯片的电源与地之间,由栅极形成的单位面积电容近似为:C/A=8.85* 10-12![]() F/m² *DK/h。

F/m² *DK/h。

——举个栗子,对于130nm工艺芯片,P/N管的片上电容约为:C/A=130 nf/cm²;65nm芯片片上电容约为:C/A=260 nf/cm²。

如下右图为250nF片上电容的阻抗曲线图。

1041

1041

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?