如何给芯片的电源网络选取合适的去耦电容呢?在前面的一篇文章中小编初步了给大家介绍了电源网络的PDN设计时去耦电容的一些基本特性,这期我们就看下如何正确的选取合适的电容。

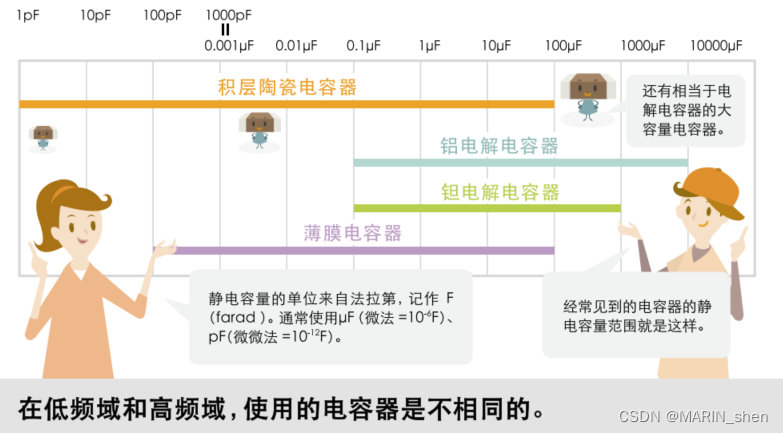

首先我们要明白一个概念就是各种电容器的静电容量范围和频带范围:下图是一个TDK的电容介绍:

不同电容器的静电容量:

按照频率使用不同的电容器:

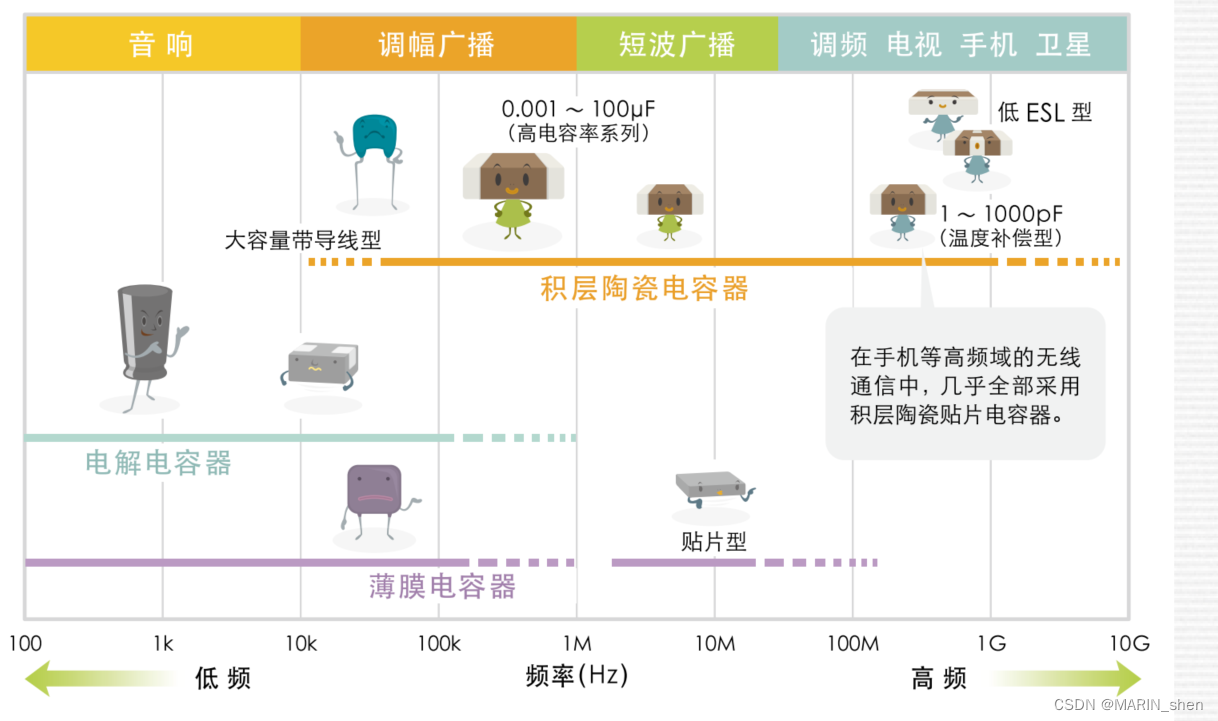

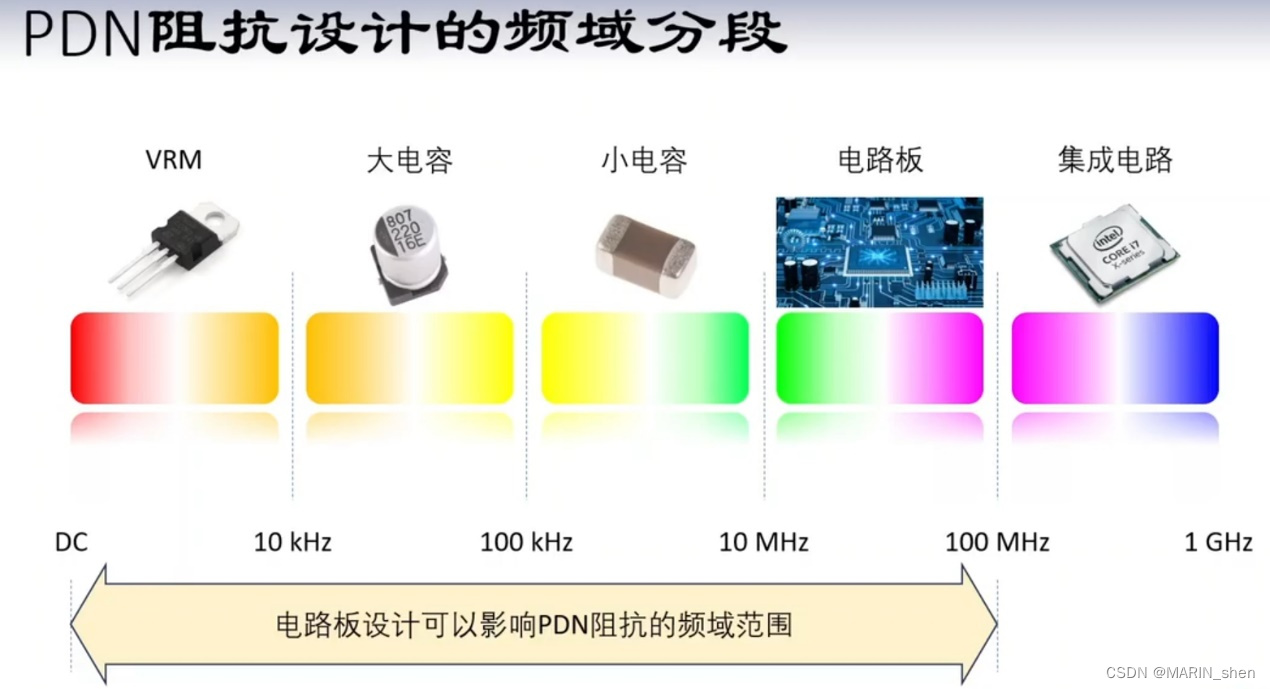

我们板子电源网络PDN设计的需要关心的频段大概是从HZ-100MHZ左右,后面的频段都是芯片级别的了,目前我们还可能使用不到。

(图片来自网上,若有特殊情况请告知删除)

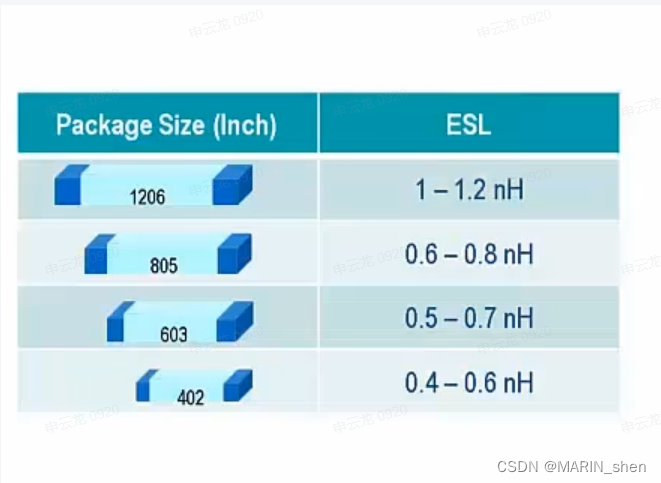

我们都知道去耦就是要选阻抗低的,阻抗低,在电容上产生的电压波动就小,也就是噪声会小。电容的容值可以通过通过额定电容量来选择,而电容的ESL与封装大小相关,一般来说电容的封装越大,自身的ESL就越大的,下图所示是一个经验值:

(图片来自网上,若有特殊情况请告知删除)

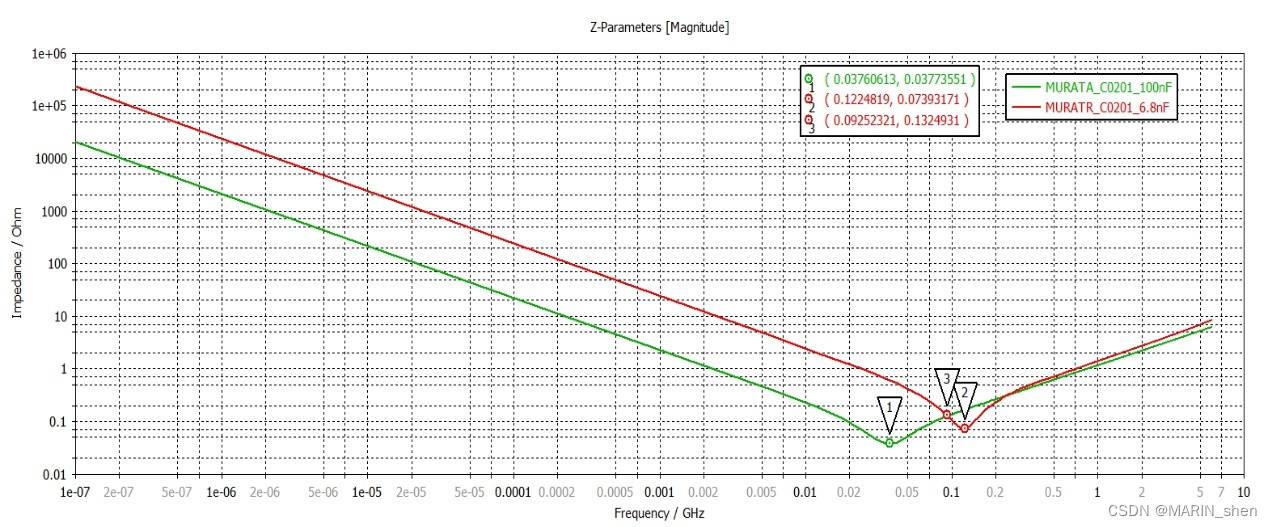

首先我们来分析一下相同封装尺寸不同容值的电容的频率特征曲线的实际情况,其中绿色曲线是0201、100nF,红色曲线是0201、6.8nF电容。

从上图我们可以得知:

- 使用电容时,如果对最小阻抗有要求,应选择ESR尽量小的电容。

- 容值越小其谐振频率点就越高。

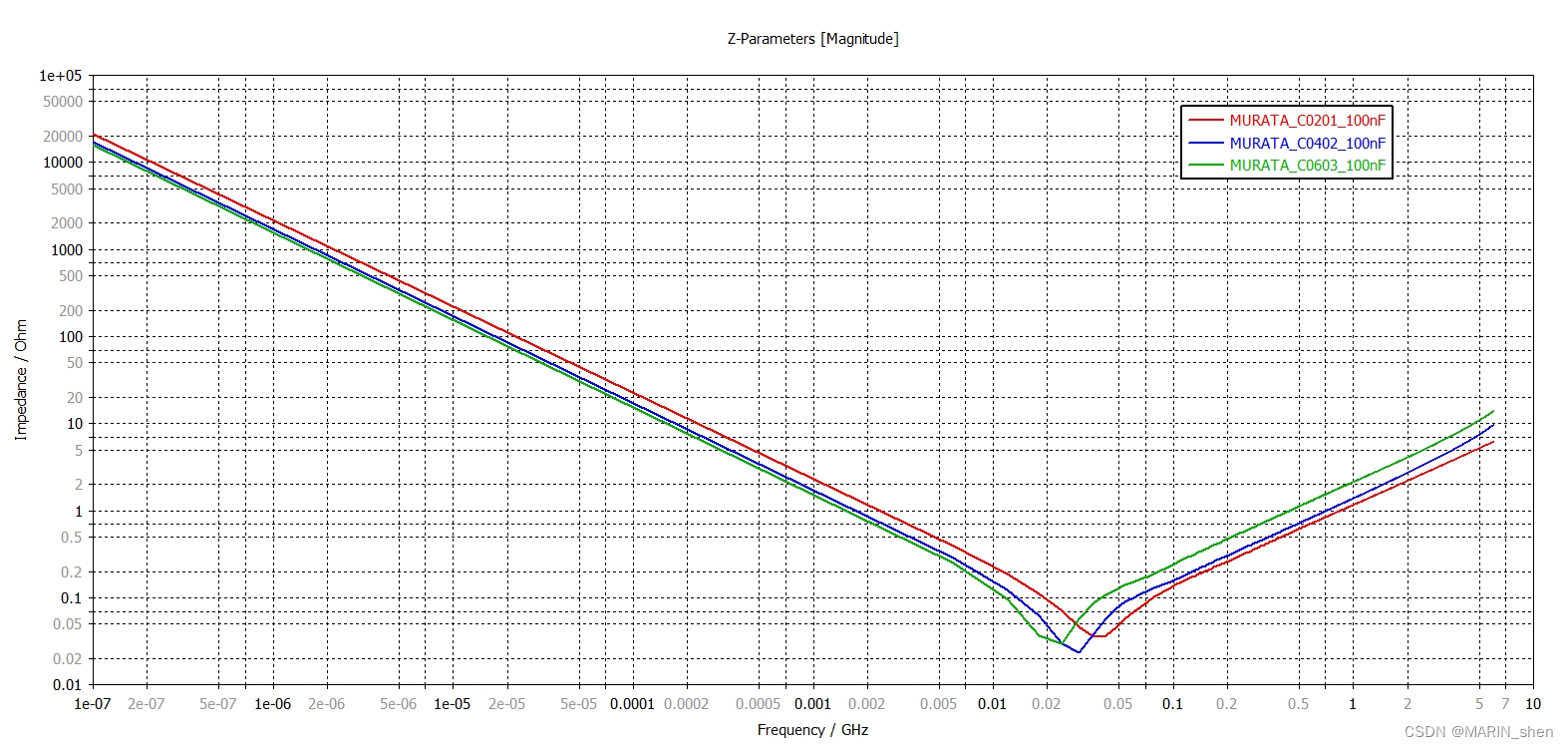

我们再来看下相同容值不同尺寸的封装的电容的频率特征曲线的实际情况,如下图所示:绿色曲线是0603、100nF电容,深蓝色曲线是0402、100nF电容, 红色曲线是0201、100nF电容。

从上图我们可以得知:

1,相同容值不同封装尺寸的电容,其电容的封装越小,其谐振频率点就越高。

2,相同容值不同封装尺寸的电容,在其谐振频率点之后,封装越大,相应的ESL就越高。

3,相同容值不同封装尺寸的电容,其电容的封装越大,其谐振频率点的ESR就越低。

4,如果对其谐振频率有要求的话,我们应选择封装尽量小的电容。

综上分析我们的电容的选取的规则:低频噪声选用大封装大电容,高频噪声选用小封装小电容。换句话说就是容量大的ESR要小一些,谐振频率低,其主要作用是滤低频噪声。容量小的ESR要大些,谐振频率要高,主要滤高频噪声。我们在选择电容组合时,如果发现了低频段的PDN偏高,可以考虑选择大容值电容。当然,电容在谐振点处的滤波特性关键还需要看ESR的大小,ESR越小,谐振点处滤波特性越好。

电容还有另外一个重要的参数就是其品质因数Q值,关于其计算公式啥的我这边就不去详细的介绍了,分享一个结果就是:一般用于电源去耦的时候,我们选择 Q 值较小的电容。一般在板级滤波的时候,会放置一些容量较大的钽电容或电解电容,这两类电容的额 Q 值较低,可以提供比较宽的有效去耦频率范围。大家对其计算推导公式感兴趣的朋友可以网上查阅一下,优先推荐你在CSDN上面找,这个网站上有很多的优质文章。

在我们的实际电路板设计中我们需要去耦的频率范围会比较宽,但是会遇到单一去耦电容不能提供一个足够低的电感值,那我们应该怎么办呢?我知道你现在可能会很急,但是请你别急,听俺说我们可以使用多个去耦电容来解决其高频去耦的问题,通常有三种方法来解决:

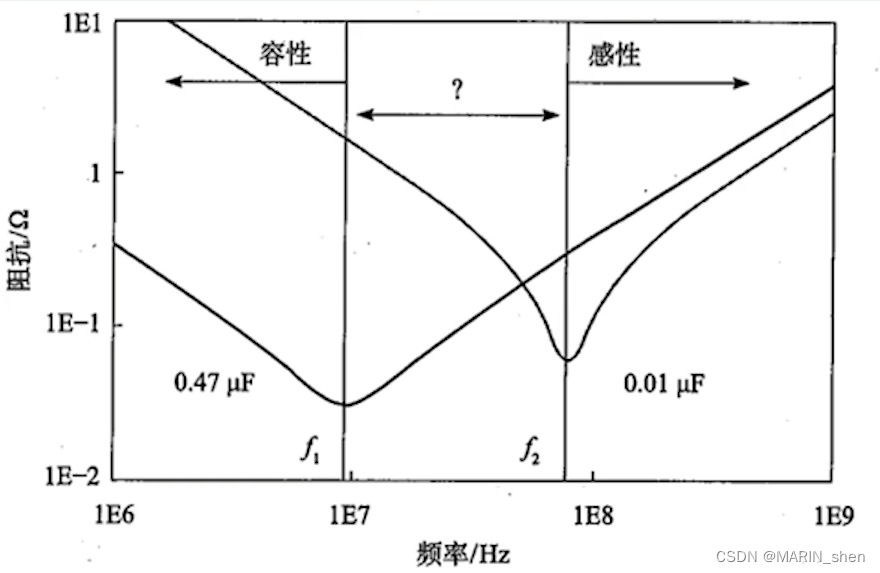

- 一种是使用一个大电容和一个小电容并联,

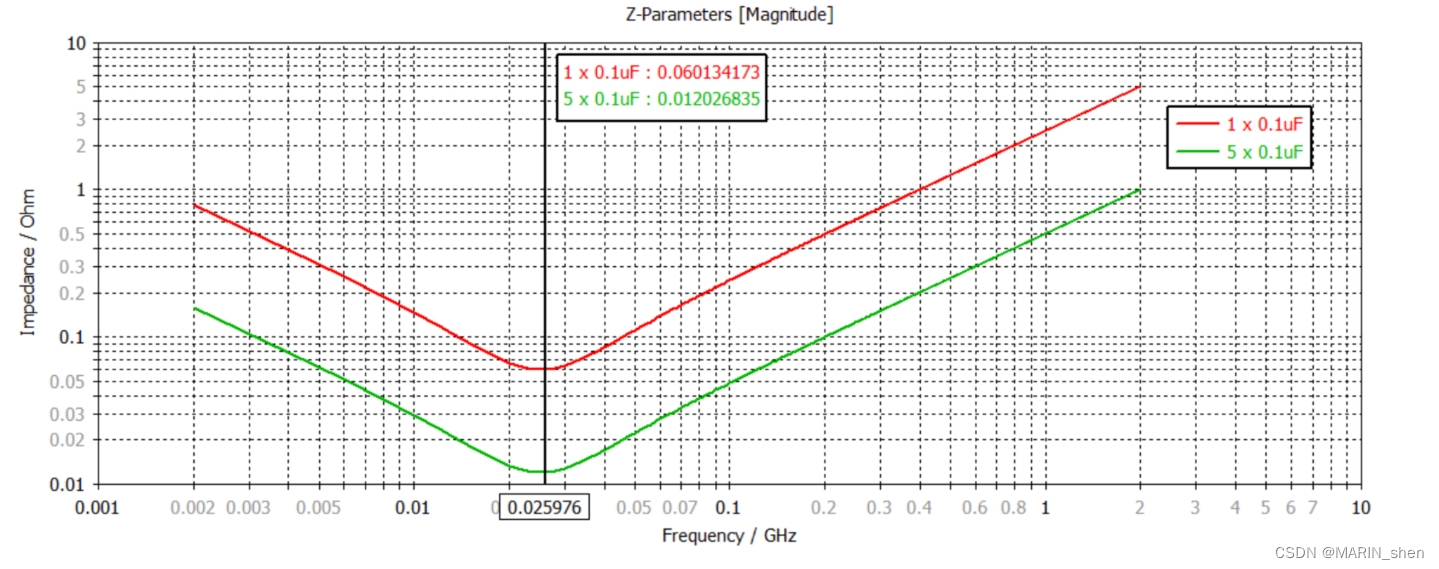

- 相同容值的 n 个电容并联合后,谐振频率不变,阻抗点的阻抗变为了原来的 1/n。

- 还有一种是使用多个相同的电容并联。(使用不同值的多个电容,通常电容值间隔10倍)

(图片来自网上,若有特殊情况请告知删除)

1,当f<fr1,两个网络均呈现容性,总电容等于两个电容之和,实际上等于大的电容值,因此,小电容对于去耦网络的性能只有较小的影响或者没有影响;

2,当f>fr2,两个网络均呈感性,总电感等于两个电感并联;

3,然而当fr1<f<fr2,则电容网络具有较大电容的感性和较小电容的容性,因此可以等效为电感和电容的并联谐振

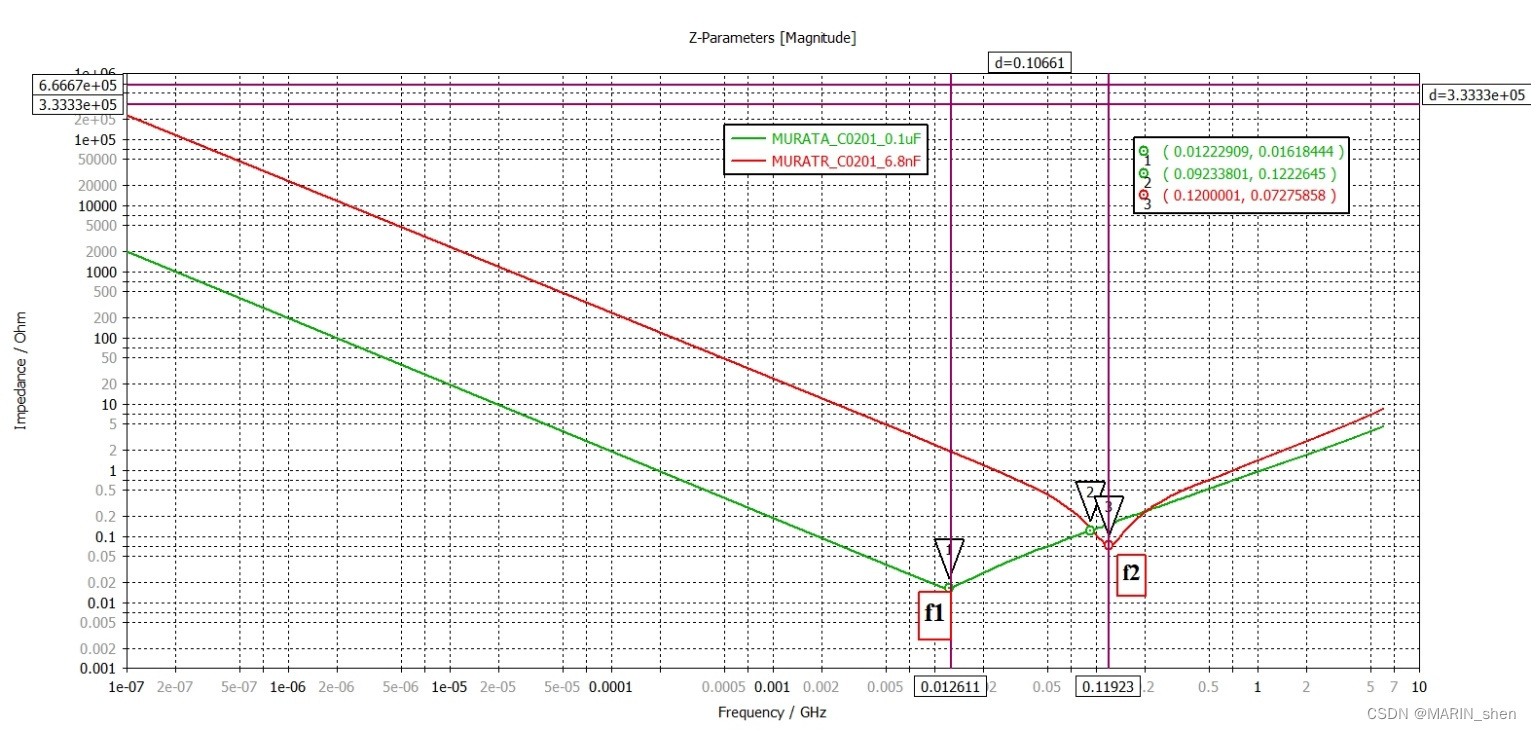

小编我本着实事求是的态度找了两个相同封装尺寸不同容值的电容通过仿真来验证一下上面的理论几乎是吻合的。

由于PDN的谐振会使得我们的信号的SI性能变差而且会使得电源对地平面的噪声也变大,如果负载芯片的电流需求正好落在这个频率,那么会导致电压波动超标。所以说PDN并联谐振也是我们需要关注的一个点。

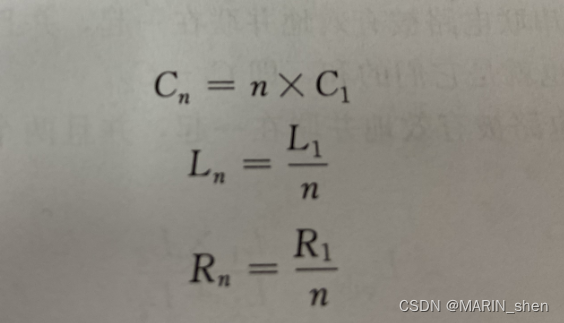

(2),相同容值的 n 个电容并联合后,其相应谐振频率是不会变的,只是阻抗点的阻抗变为了原来的 1/n,这个也是有公式推导出来的如下图所示:

其中C1是RLC模型中单个电容器件的电容值;L1是RLC模型中单个电感器件的电感值;

R1是RLC模型中单个电阻器件的电阻值;Cn是与N个RLC电路并联时的阻抗相同的单个RLC模型中的等效电容;Ln是与N个RLC电路并联时的阻抗相同的单个RLC模型中的等效电感;Rn是与N个RLC电路并联时的阻抗相同的单个RLC模型中的等效电阻。

实际的仿真结果:

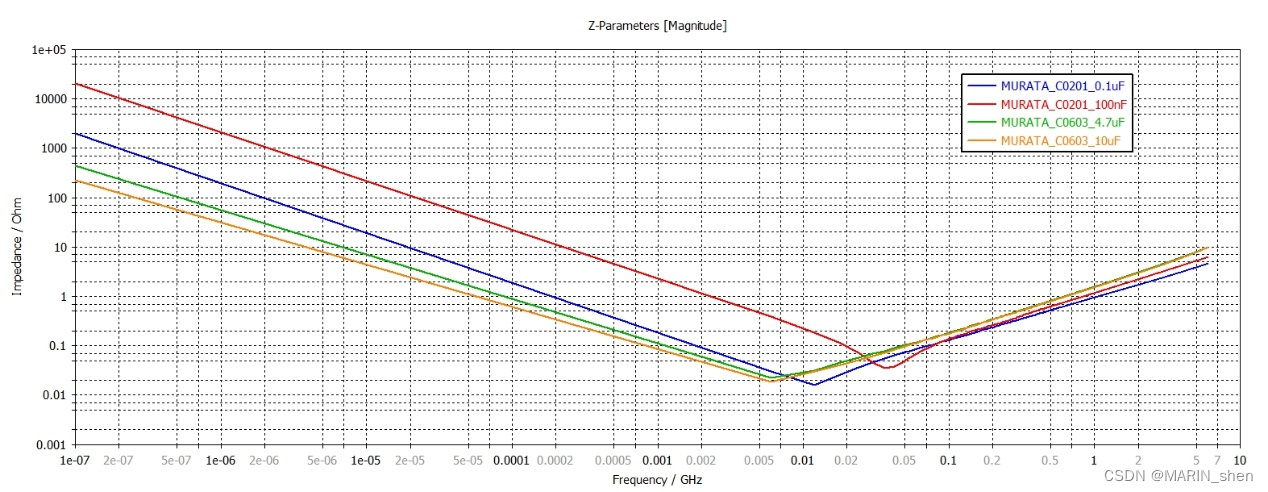

(3)当使用多个不同值的电容组合搭配后,从结果来看确实可以拓宽其低阻抗的曲线范围,但是其电容的反谐振现象是依然存在的。

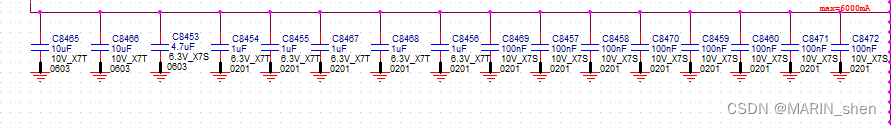

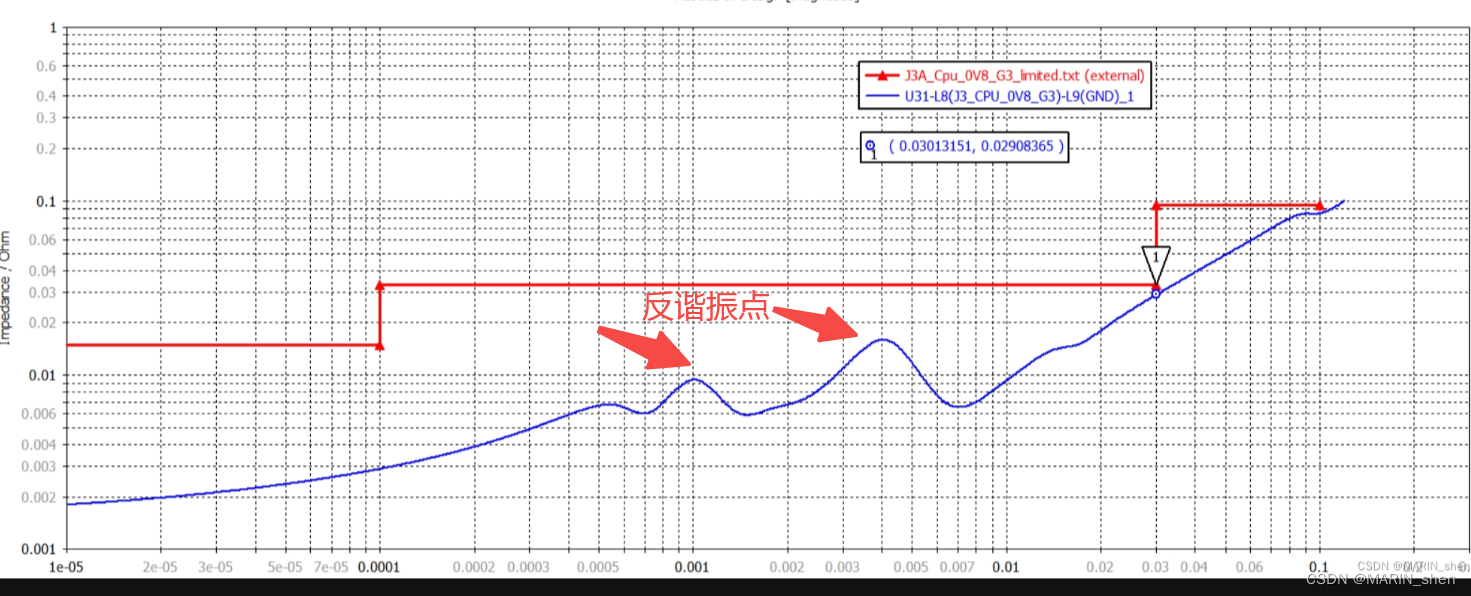

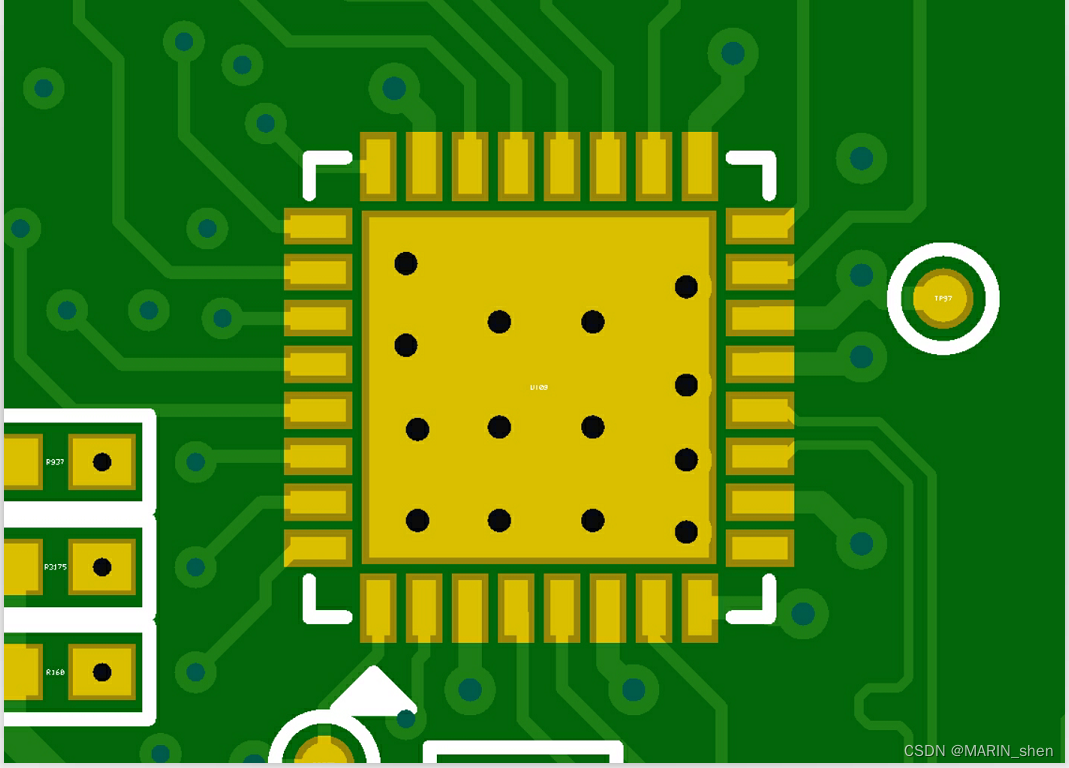

我们带入到实际的项目中来看,小编我找了个之前设计电路板上的主芯片的CORE电源来给大家简单的分析一下:

其core电源的原理图设计如下:

仿真结果图下图所示:

虽然电源网络的反谐振现象依然存在的,但是要保证反谐振阻抗小于你的电源网络的PDN目标值也是没有多大问题的,切记曲线尽量不要压着边过,留一些阻抗的裕量是比较好的。

如何选取合适的电容就像你单身的时候找女朋友一样,虽然路上困难重重,但是方法还是有的啊。多想想总能够找到问题的答案的,好了以上就是这期的内容了,下期文章小编将会分享一些关于PDN设计时其电容上寄生电感和回路电感的设计经验。

175

175

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?