摘要:EMIO与pin连接;GPIO通过EMIO映射到sysfs;FPGA配置方式,通过zu67向ku3p下载bit文件

1. EMIO与pin连接

MIO,Multiuse I/O,称为复用输入/输出,对应PS侧的可配置的多功能引脚。

EMIO,Extent MIO,称为扩展复用输入/输出,对应PL侧的可配置的多功能引脚。

MIO是外设的基础引脚,因为MIO引脚数量较少,ZYNQ也提供了EMIO接口作为MIO的扩展,外设可通过EMIO接口路由到PL侧的引脚上,来实现与MIO几乎相同的功能。

几乎相同也就意味着有些许不同,MIO和EMIO作为引脚不同的地方有3点:

1.MIO对于PL侧是透明的,PL无法得到MIO引脚上的电平信息,而EMIO因为就是PL的引脚,所以PS可以通过EMIO与PL通信

2.外设与MIO是固定搭配的,就是说要使用MIO作为外设引脚就必须是一组固定引脚。如下图,举个例子,如果你使用了MIO34作为UART0的一个引脚,那么UART0的另一个引脚必须是MIO35,USB1也是如此,除了GPIO比较特殊外,其它外设MIO都是一组一组起作用的,并且是产商预先定好的位置,不能任意指定,所以在设计硬件电路时,使用哪些引脚来连接外设要遵照这一特性。另外因为电路是确定的,使用MIO也不用指定引脚约束。

EMIO相对灵活,引脚之间预先没有绑定,可任意指定,而且使用EMIO需要加引脚约束指定到PL确定的某个引脚。

以上文字我摘录来源于:ZYNQ7000-MIO与EMIO详解_徐晓康的博客的博客-CSDN博客

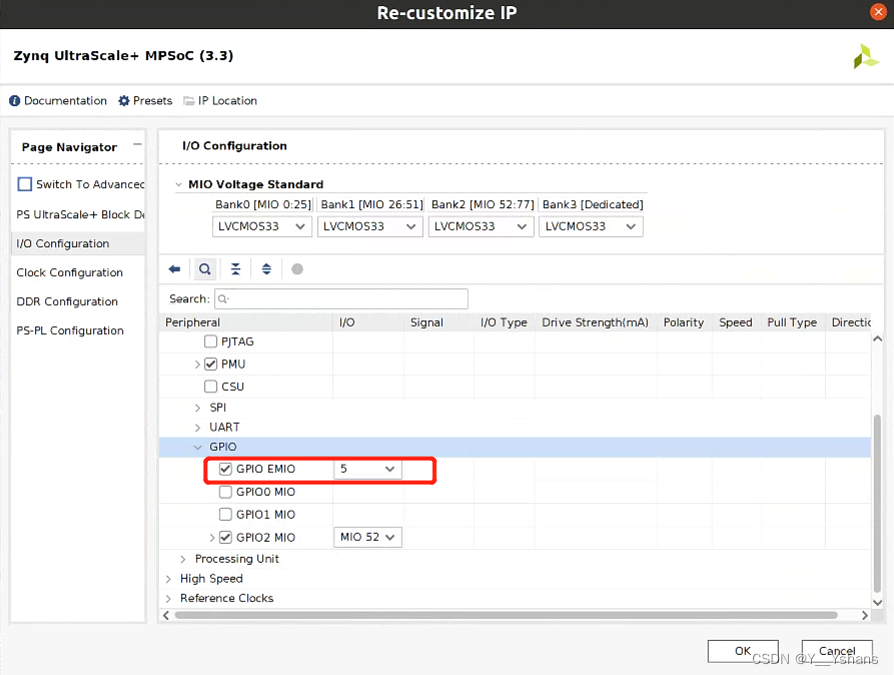

在zu67上,zynq直接勾选就行

EMIO与pin连接应该是有两种方式:

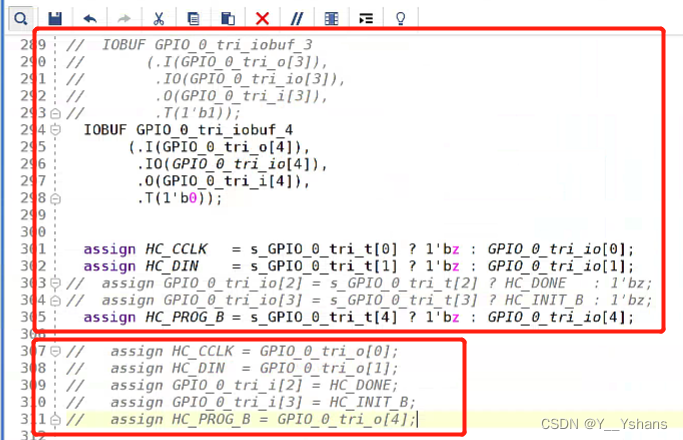

第一种通过IOBUF,但是这种方式只能直接连接inout类型的pin

第二种直接input连接input,output连接output,按照EMIO顺序连接pin就可以

最后上版调试的时候发现一个问题,如果HC_PROG_B由EMIO来提供值得时候,此时软件并未对这个值做任何处理,那么EMIO给的默认值是0(拉成1或者z就能解决)。这个时候,调试会出现问题,vivado会错误识别芯片。

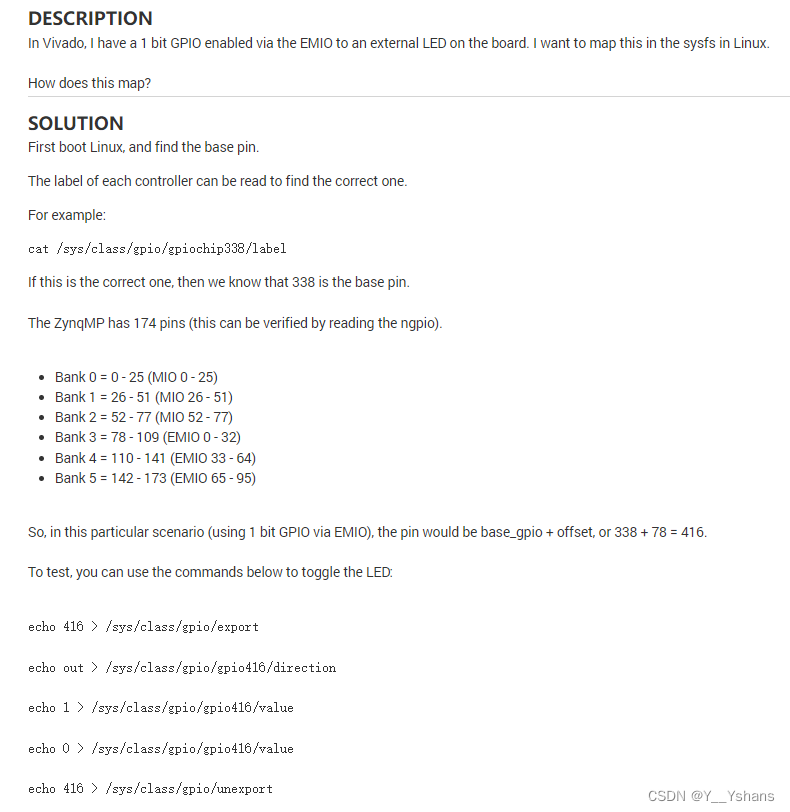

2. GPIO通过EMIO映射到sysfs

3. FPGA配置方式

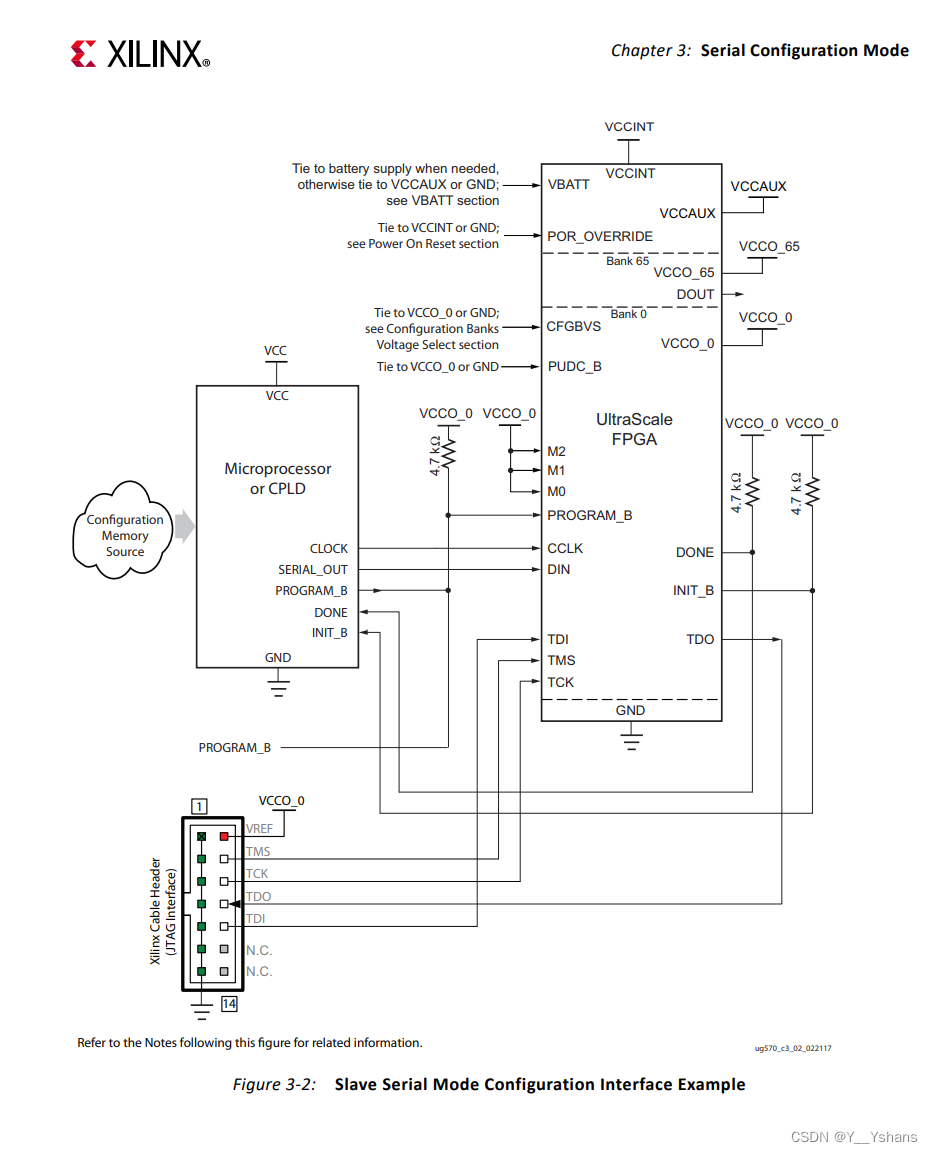

我的使用场景就是通过zu67向ku3p实现bit下载(逻辑由软件实现)

需要注意:

PROG_B如果一直为1 FPGA是在复位态

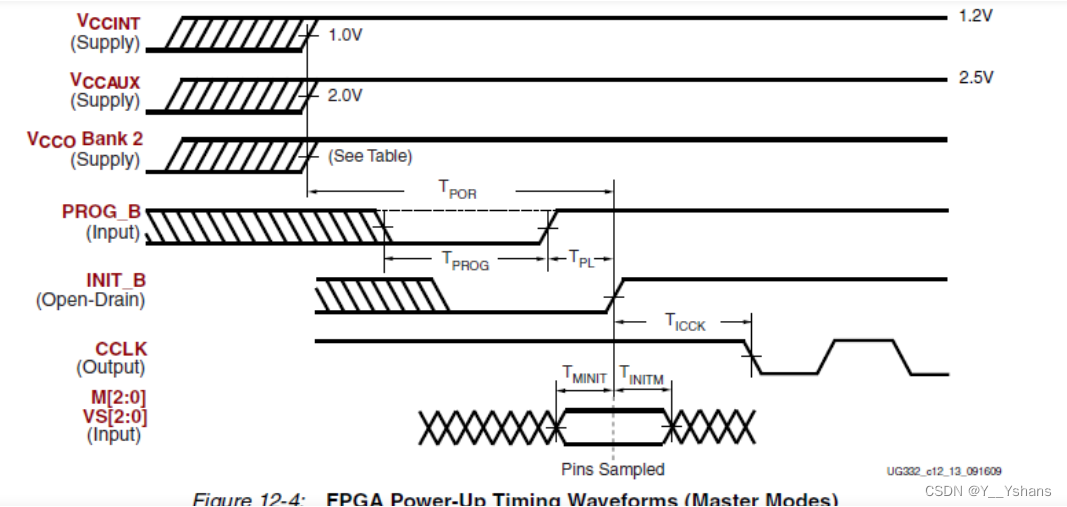

(1)FPGA上电后,仅仅有在内核电压、參考电压、IO口电压都正常的情况下,才进入配置模式;

(2)下拉PROG_B。FPGA复位。同一时候对配置存储空间进行初始化;

(3)将INIT_B。DONE管脚信号拉低,DONE信号与PROM芯片的CE管脚信号相连。从而使PROM片选信号有效;INIT_B为低,指示电源供压正常,FPGA正处于配置存储空间初始化中;

(4)FPGA在PROG_B管脚信号变为高电平时,開始配置过程;

(5)FPGA在INIT_B上升沿中读取配置管脚M[2:0]的值,从而确定FPGA的配置模式。

(6)PROM通过Do管脚将配置数据以CCLK时钟信号的速率传给FPGA

(7)配置完毕后。将DONE管脚信号置为低电平,指示配置已经完毕。

总结

学无止尽

1019

1019

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?