文章目录

高动态范围(HDR)

许多应用,如汽车成像、监视和科学,都会遇到图像中最亮和最暗部分之间存在很大差异的场景。传感器的动态范围(DR),定义为其FWC与读出噪声的比率,必须超过 1 0 5 10^5 105甚至 1 0 6 10^6 106,才能忠实地捕捉那些具有挑战性的场景。为了解决这个问题,已经开发了各种具有高动态范围(HDR)的CIS,通常意味着高于 1 0 5 10^5 105 (100dB)。

典型的PPD像素在1000 (60db)到10000 (80db)之间实现DR,这取决于像素大小、转换增益和系统噪声。快速计算可以显示为什么80db以上的DR难以实现。一个5 μm像素可以有60%的填充系数和 2 k e − μ m − 2 2ke^-μm^{-2} 2ke−μm−2的面积容量,因此它可以存储 30 k e − 30ke^- 30ke−。对于1.5 V的最大输出信号,转换增益不得超过 50 μ V / e − 50μV/e^- 50μV/e−,噪声可能在 4 e − 4e^- 4e−RMS左右,因此最大DR为30000/ 4 = 7500 (77.5 dB)。

降低读出噪声似乎是提高DR的好方法,并且已经开发出具有非常低甚至亚电子噪声的PPD成像仪。然而,降低噪声的代价是将转换增益提高到 100 μ V / e − 100 μV/e^- 100μV/e−以上,而最大输出信号仍然不能超过1.5 V左右。因此,FWC受到输出信号的限制,而不是PPD的FWC, DR也不会有很大的飞跃。例如,[35]中的像素实现了 0.5 e − 0.5 e^− 0.5e−RMS的读出噪声,但在82 dB的DR下实现了 6400 e − 6400 e^− 6400e−FWC,而[36]中的 0.27 e − 0.27 e^- 0.27e−RMS像素仅管理了75 dB。

另一种增加DR的“简单”方法——提高FWC和输出信号跨度,也不是很有效。在新的CMOS工艺中,工作电压往往更低,像素也会缩小,使得PPD面积和FWC更低。此外,HDR需要16位以上的片上ADC分辨率,这是一个很大的挑战。

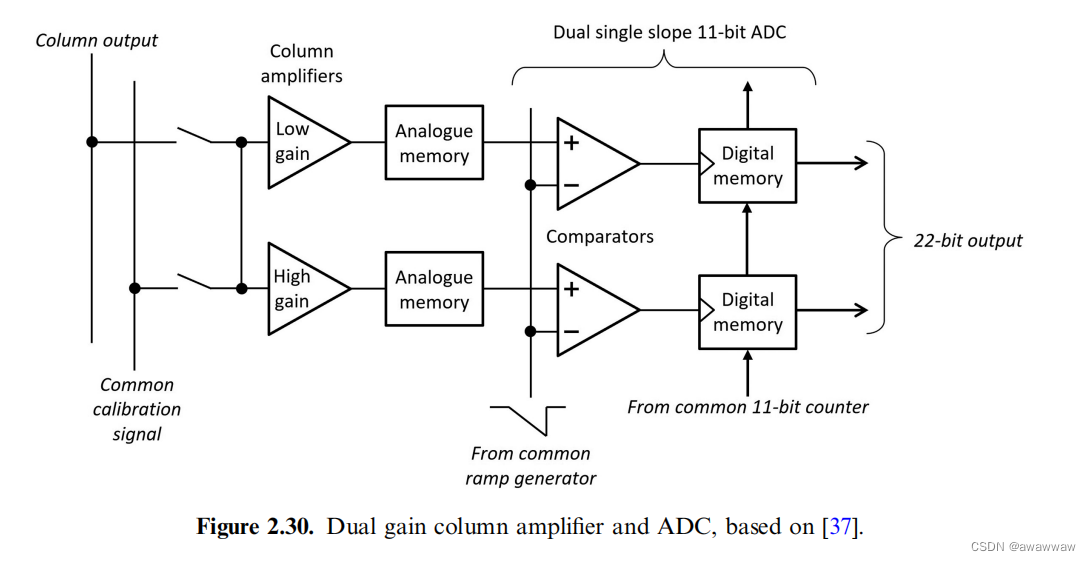

由于低噪声像素中的最大饱和信号受到读出路径的限制,而不是PPD的FWC,因此HDR的解决方案通常在于列读出电路,而不是新的像素架构。一个非常成功的解决方案是采用双ADC转换的双增益列放大器,如图2.30所示。在这里,一个低噪声5T像素图像阵列由两个列放大器提供:一个增益为1,另一个增益为30,它们的输出由单独的11位adc数字化。每个信号处理通道的DR仅为64 dB(高增益)和74 dB(低增益),但合并后的DR为92 dB,噪声仅为 1.2 e − 1.2 e^− 1.2e−RMS。使用类似架构和进一步改进的CIS已经刺激了“科学CMOS”(sCMOS)图像传感器的非常成功的产品线,用于许多高性能应用。

对传感器进行多次曝光是实现高DR的最有效方法之一,而且不需要新的像素。多次曝光也是最古老的HDR方法,从摄影胶片时代就开始使用。基于该方法的许多技术已经被发明并在4T和5T像素上实现,如部分电荷转移(“电荷撇读”)、多子帧读出和交错曝光。这些技术的一个共同特点是,由于曝光发生在不同的时间,它们容易受到运动伪影的影响;这在快速移动的场景中是有害的,特别是在汽车成像中。

考虑到具有HDR功能的像素架构,单次曝光是更可取的,因为运动伪影被最小化。线性响应也是首选;对数像素可以覆盖超过120 dB的光照水平,但反应时间较慢,时间和固定模式噪声较差。

进一步的考虑只给线性像素,分为三个主要类别:

- 双光电二极管

- 多像素内增益

- 溢出信号存储

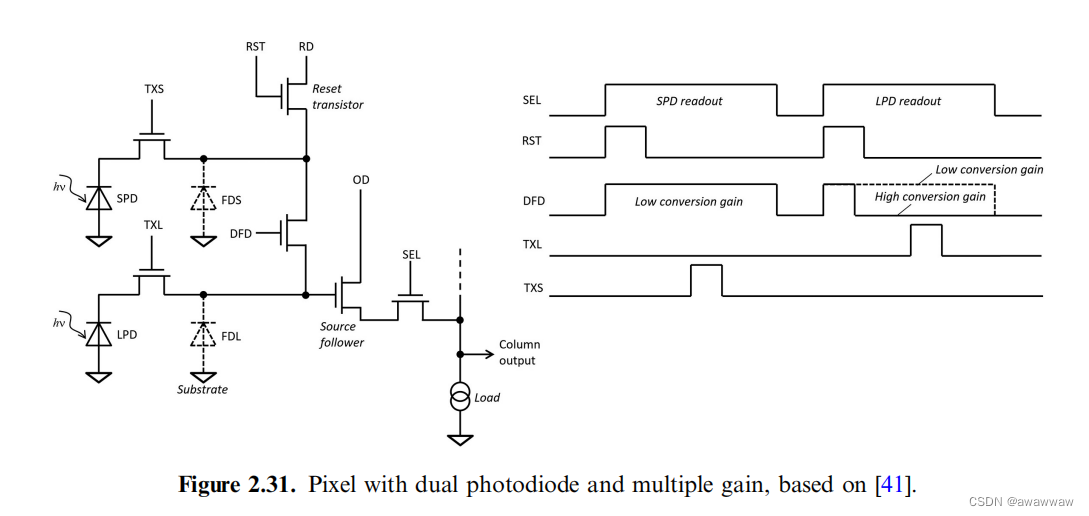

图2.31中的像素使用两个固定的光电二极管,灵敏度比为6.5:1。晶体管开关(DFD)连接两个检测节点FDL和FDS,当激活时,由于它们的组合电容,转换增益降低。光电二极管SPD以低转换增益读出,而LPD可以同时使用两种增益。3路读数,加上一个复杂的ADC和数字外围,导致DR超过120 dB,读出噪声为0.94 e - RMS。

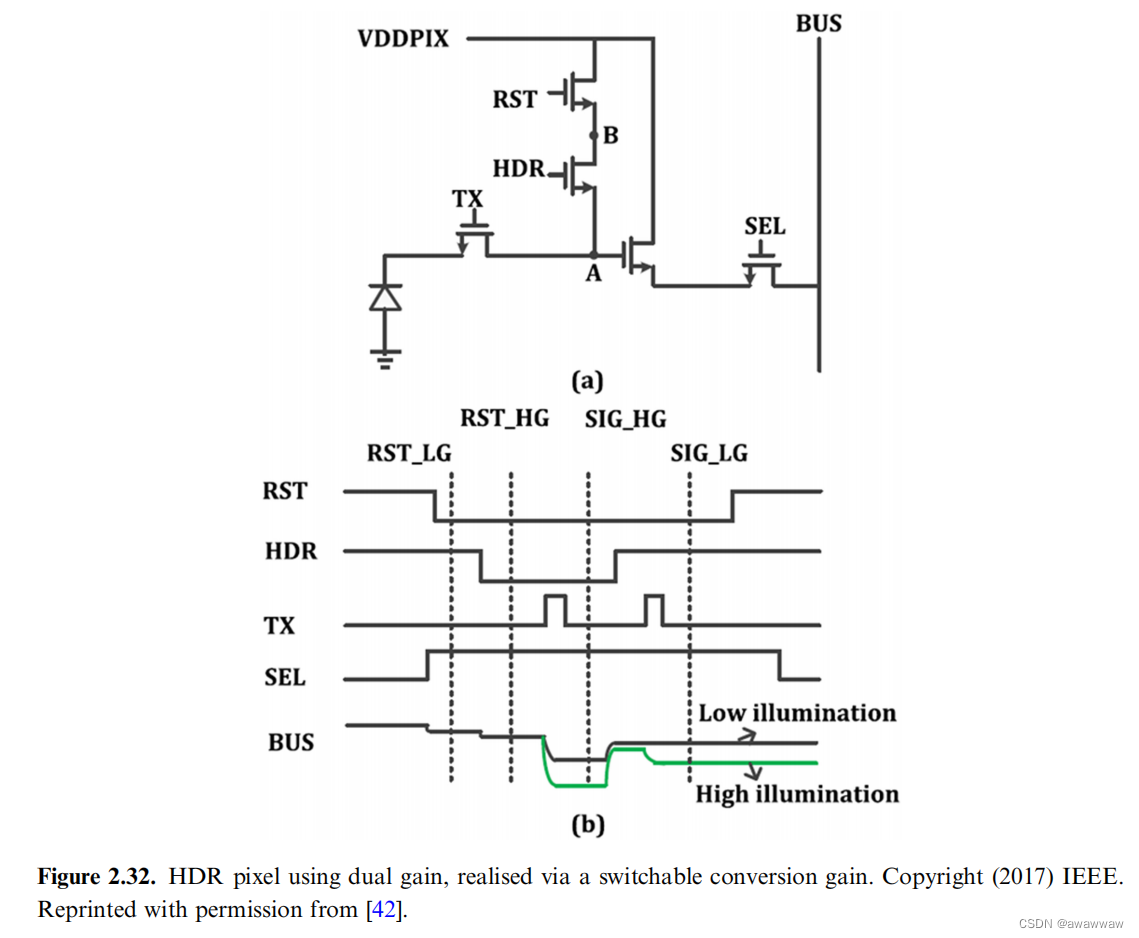

具有双像素和三像素增益的HDR方法,以及只有一个PPD,也显示出非常好的性能。图2.32中的像素使用晶体管HDR将B点的电容与感测节点(A点)的电容相加,以减小转换增益。根据时序图以低增益(LG)和高增益(HG)测量信号两次,动态范围为87 dB,噪声为2.0 e−RMS。使用三倍增益时,DR增加到91 dB,双增益和双曝光的组合将DR提高到令人印象深刻的120 dB。

横向溢流集成电容器(LOFIC)是HDR成像最优雅的解决方案之一。LOFIC像素于2005年发明并经过进一步改进,其工作原理是允许电荷从PPD溢出,通过转移门进入高值信号存储电容器。通过这种方式,PPD的FWC不是一个限制因素,并且DR大大增加,因为存储电容器使用薄栅氧化物以获得最高可能的密度。LOFIC将图2.32中的设计向前推进了一步,并保留了低感测节点电容以获得非常高的转换增益,同时也允许在单次曝光中测量大信号。

如图2.33所示,积分过程中M3开启。任何电荷溢出转移门M1产生的阻挡,最终在t3时刻进入感测节点FD和存储电容CS的组合电容中。对于高增益读出M3被关闭,剩余的PPD电荷通过脉冲在t5中传递到检测节点。低增益信号读出是通过再次打开M3来完成的,这样FD和CS上的所有电荷都被检测到。

小信号不超过PPD的FWC,读取类似于正常的4T像素。CDS是通过在步骤t2中读取感知节点的复位电平来完成的。LOFIC方法以非常低的噪声实现了超过100 dB的HDR,并且已经证明了两级设计的DR为120 dB。

还有更多HDR概念存在,设计师的聪明才智也没有明显的限制。其中最具创意的一种方法是同时使用电子和空穴收集,分别应用不同的转换增益,在3.2 μm像素内实现115 dB的DR。

参考书目:

- CMOS image sensor,Konstantin D Stefanov,2022

本文探讨了高动态范围(HDR)技术在图像传感器领域的应用,介绍了如何通过改进像素架构、双ADC转换、多次曝光和创新设计(如LOFIC)来解决传感器动态范围问题。这些方法提高了传感器的DR,尽管面临低噪声和输出信号限制等挑战。

本文探讨了高动态范围(HDR)技术在图像传感器领域的应用,介绍了如何通过改进像素架构、双ADC转换、多次曝光和创新设计(如LOFIC)来解决传感器动态范围问题。这些方法提高了传感器的DR,尽管面临低噪声和输出信号限制等挑战。

7880

7880

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?