D-PHY(Digital Physical Layer)是MIPI(移动产业处理接口)联盟制定的一种高速串行接口技术规范,主要用于移动设备和嵌入式系统中的显示屏和摄像头等外设的连接。其硬件结构复杂且功能多样,以下是其主要组成部分及其工作原理:

-

通道模块:

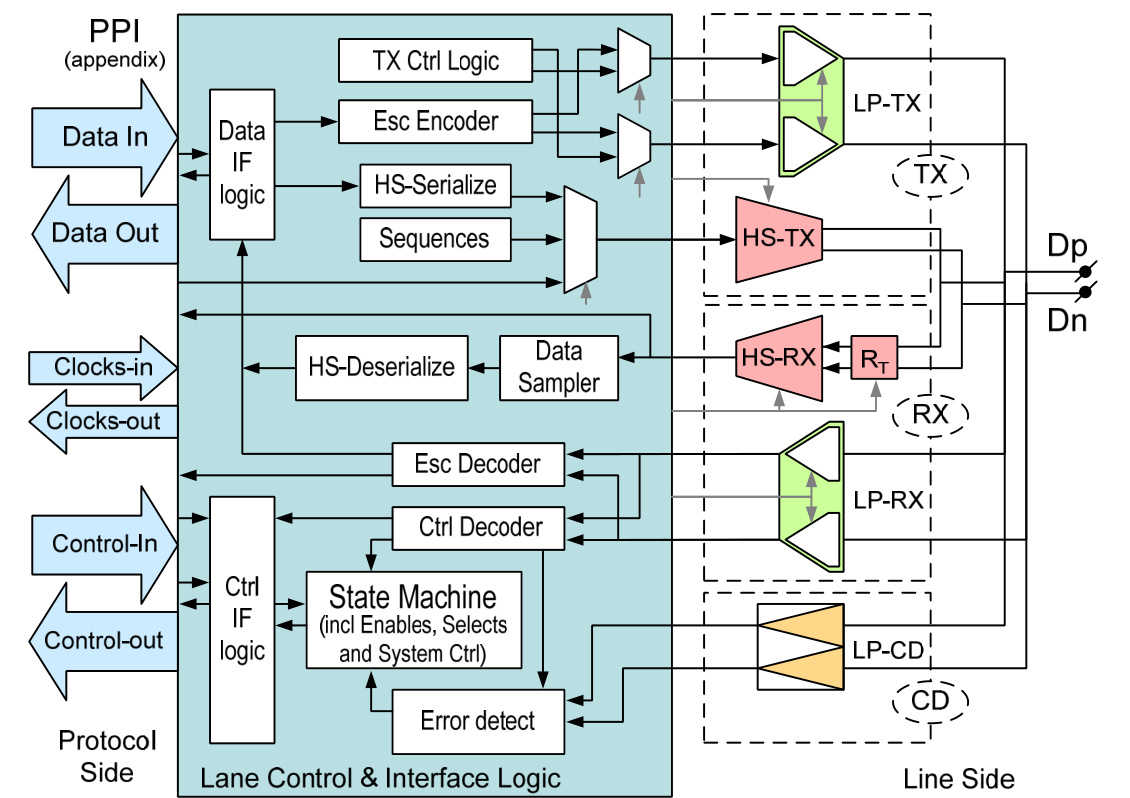

- 每个通道由多个子模块组成,包括低功耗发射器(LP-TX)、低功耗接收器(LP-RX)、高速发射器(HS-TX)、高速接收器(HS-RX)以及低功耗竞争检测器(LP-CD)。

- 数据传输采用DDR方式,在时钟的上下边沿都有数据传输,支持高速(HS)和低功耗(LP)两种工作模式。

-

同步时钟通道:

-

D-PHY采用1对源同步差分时钟和1~4对差分数据线进行数据传输,这意味着每个通道包含一个同步时钟通道和若干个数据通道。

-

包含多个状态机和控制逻辑单元,用于管理数据流、错误检测和纠正等功能。

-

-

电气特性:

- 支持多种电气特性,如绝对最大范围、推进动作条件下的电气特性、电源管理、热插拔特性、ESD保护等。

-

物理层设计:

- D-PHY的物理层设计包括四个数据通道和一个时钟通道,每个数据通道可以独立配置为高速模式或低功耗模式。例如,某些实现支持单向高速模式最高可达8 Gbps,双向低功耗模式每条通道速率为10 Mbps。

-

接口与协议:

- 支持MIPI DSI(Display Serial Interface)和CSI-2(Camera Serial Interface 2)链路层协议,适用于摄像头和显示器的接口。

-

集成与兼容性:

- MIPI D-PHY IP提供灵活的通道设计,满足现代SoC的需求,并确保了与其他MIPI标准如CSI-2和DSI的互操作性。

-

应用领域:

- 主要用于移动设备如智能手机和平板电脑中的显示屏和摄像头接口,提供高带宽、低功耗和可靠性的特点。

通过上述分析可以看出,D-PHY硬件结构不仅包含复杂的物理层设计和多种功能模块,还具备高度的灵活性和兼容性,以适应不同应用场景的需求。

D-PHY硬件结构中的低功耗发射器(LP-TX)和接收器(LP-RX)的工作原理是什么?

D-PHY硬件结构中的低功耗发射器(LP-TX)和接收器(LP-RX)的工作原理如下:

低功耗发射器(LP-TX)

- 工作模式:LP-TX在低功耗状态下工作,用于驱动信号以维持线路的通信状态。

- 信号类型:LP-TX使用单端低电压摆幅(Low-Voltage Swing, LVS)单向信号传输。这种信号传输方式比高速模式下的差分信号传输具有更低的功耗。

- 激活条件:只有当需要进入低功耗状态时,LP-TX才会被启用。这意味着它不会在所有时间都处于活动状态,而是根据需要进行切换。

- 功能要求:LP-TX的主要任务是确保在低功耗模式下能够可靠地维持数据传输,同时尽量减少功耗。

低功耗接收器(LP-RX)

- 工作模式:LP-RX同样在低功耗状态下工作,用于检测线路上的低功耗状态并响应相应的信号。

- 信号类型:LP-RX也采用单端低电压摆幅(LVS)单向信号接收。这与高速模式下的差分信号接收不同,有助于降低功耗。

- 噪声过滤:为了提高鲁棒性,LP-RX设计中包括了噪声脉冲和射频干扰的过滤机制。当输入的噪声脉冲小于eSPIKE阈值时,LP-RX会将其拒绝。

- 阈值监测:LP-RX需要持续监控线路电平,并且能够检测到不同阈值范围内的信号变化。这些阈值包括最低低电平、最高高电平等关键参数,以确保在不同的操作条件下都能正确工作。

共同特性

- 成对出现:低功耗功能总是成对出现,即每个通道上都有对应的LP-TX和LP-RX来分别处理低功耗和高速信号。

- 双向操作:如果存在双向操作需求,还需要一个低功耗争用检测器(LP-CD),用于在LP-TX驱动低功耗状态时检测争用情况。

如何实现D-PHY同步时钟通道以提高数据传输的准确性和可靠性?

要实现D-PHY同步时钟通道以提高数据传输的准确性和可靠性,可以采取以下措施:

-

使用主从间源同步接口:D-PHY提供了主从间源同步接口,包含1对单向差分时钟,支持SSC(Source Synchronization Control)。这意味着在主设备和从设备之间可以进行时钟同步,确保数据传输的同步性。

-

采用DDR方式的数据传输:数据传输采用DDR(Dual-Difference Differential)方式,即在时钟的上下边沿都有数据传输。这种传输方式可以提高数据传输的准确性和可靠性。

-

实施错误检测和纠正机制:为了提高数据传输的可靠性,可以采用错误检测和纠正技术,如奇偶校验、循环冗余检查(CRC)和扭曲码等。这些技术可以在传输过程中检测和纠正错误,以确保数据的完整性和准确性。

-

使用冗余数据:使用冗余数据也是提高可靠性的一种方法。通过增加额外的数据副本,可以在数据丢失或损坏时提供备份,从而提高数据传输的可靠性。

-

时间同步协议:参考Intel® 82579 Gigabit Ethernet PHY产品特性中提到的IEEE1588和IEEE802.1AS协议,用于确保时间同步。这些协议支持系统级同步精度在亚微秒范围内,并具有简单的空间本地化特性,无需用户管理即可安装和运营。

-

时钟通道的控制与管理:根据MIPI Alliance Specification for D-PHY,时钟通道由协议通过时钟通道PPI控制,当没有活动的高频传输时,协议将停止时钟通道。这有助于在低功耗模式下减少功耗,同时保持时钟信号的稳定性。

-

数据传输协议和技术的选择:选择可靠的数据传输协议和技术至关重要,如TCP/IP协议以及数据包重传机制,以应对网络故障、丢包等问题。

D-PHY状态机与控制逻辑单元是如何管理数据流、错误检测和纠正的?

D-PHY状态机与控制逻辑单元在管理数据流、错误检测和纠正方面的工作原理可以从多个角度进行解析。

数据流管理

D-PHY的状态机负责管理数据流的传输。例如,在发送端,D-PHY会根据特定的状态码(State Code)来定义状态转换,从而确保数据能够按照正确的顺序和格式进行传输。具体来说,D-PHY通过设置不同的控制位(如FTXSMDL和FTXSMCL)来强制控制某些状态和行为,例如在TX停止模式下将数据通道或时钟通道置于传输控制模式并开始传输停止状态(LP-11)。这些控制位允许微控制器对D-PHY进行精确的配置和控制,以满足不同的应用需求。

错误检测

D-PHY具备一定的错误检测能力。它可以在SoT(Start of Transmission)和EoT(End of Transmission)过程中检测到某些错误,并触发中断信号(IRQ),从而通知系统进行相应的处理。此外,D-PHY的数据包中包含校验码(CRC),可以用于检测出一个或多个错误,但不能直接纠正这些错误。这种机制确保了数据在传输过程中的完整性,尽管需要额外的步骤来纠正检测到的错误。

错误纠正

虽然D-PHY本身具备基本的错误检测功能,但其主要的错误纠正机制依赖于高层协议或软件层的支持。例如,在CSI-2协议中,长包和短包都包含有校验码,能够进行误码纠正和错误检测。这意味着在硬件层面,D-PHY仅负责检测错误,而具体的纠正工作则由上层协议或软件完成。

总结

D-PHY状态机与控制逻辑单元通过一系列复杂的控制位和状态转换来管理数据流,确保数据能够正确传输。同时,它利用校验码等机制进行基本的错误检测,但实际的错误纠正通常需要依赖于更高级别的协议或软件实现。

D-PHY支持哪些具体的电气特性,如ESD保护、热插拔特性等,以及这些特性的具体实现方式是什么?

D-PHY支持的电气特性包括ESD保护和热插拔特性,具体实现方式如下:

-

ESD保护:

- D-PHY接口设计中包含了ESD保护机制,以防止静电损害。中提到的Common mode filter with ESD protection for MIPI D-PHY and MDDI interface,表明D-PHY接口在设计时考虑了ESD保护,通过使用具有高共模衰减的滤波器来减少ESD对信号的影响。

- 中提到的双通道MIPI® DSI 转双链路FlatLink™ LVDS 桥接器,其ESD等级为±2kV (HBM),说明D-PHY接口能够承受较高的ESD电压,确保设备在恶劣环境下正常工作。

-

热插拔特性:

- 中提到的max9295热插拔技术,基于MIPI D-PHY规范,支持最高达5Gbps的数据传输速率,并且可以实现在运行时连接和断开多个设备,而无需重新启动整个系统。这表明D-PHY接口设计了热插拔功能,允许在不干扰系统运行的情况下添加或移除设备。

- 中GW5AT系列FPGA产品数据手册也提到了热插拔特性,进一步证实了D-PHY接口支持热插拔功能。

MIPI D-PHY IP在不同应用场景中的集成与兼容性是如何保证的?

MIPI D-PHY IP在不同应用场景中的集成与兼容性主要通过以下几个方面来保证:

-

标准规范的遵循:MIPI D-PHY IP严格遵循MIPI组织制定的一系列标准规范,以确保移动设备和组件之间的互通性和兼容性。例如,T2M-IP发布的MIPI D-PHY v2.5 Tx和DSI Tx控制器v1.2完全符合MIPI D-PHY v2.5规范,确保与其他兼容设备的无缝集成和互操作性。

-

工艺节点的适应性:MIPI D-PHY IP在多个工艺节点上进行了硅验证,并广泛应用于汽车应用芯片组,如M公司的MIPI D-PHY IP已经在多个工艺节点和铸造厂进行了硅验证。此外,T2M-IP的D-PHY IP在各种铸造工艺中都配备了标准兼容性。

-

IP核的集成与简化开发流程:Xilinx提供的MIPI D-PHY硬核IP可以直接集成到设计中,简化了开发流程。Arasan的D-PHY IP与自己的MIPI DSI-2和CSI-2 IP无缝集成,提供完整的MIPI显示和摄像头IP解决方案。

-

支持多种模式和接口:MIPI D-PHY功能支持高速(HS)和低功耗(LP)模式,可直接与D-PHY合规组件相连,无需外部组件,支持每通道速率高达3.5 Gbps的信号传输,并支持AXI-Lite接口实现无缝视频传输和接收。

-

测试与验证:MIPI D-PHY IP经过各种测试场景的支持,包括生产测试和特性测试,以确保其在实际应用中的可靠性和性能。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?