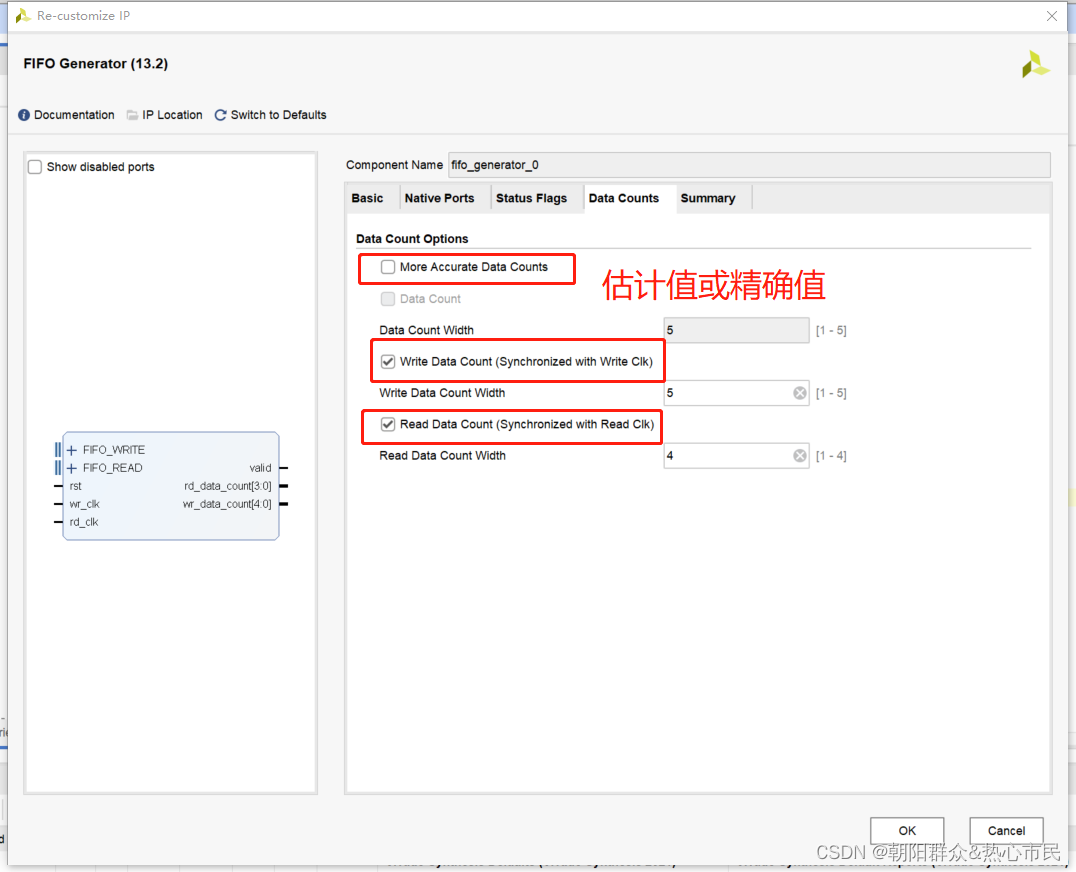

fifo IP核设置读写个数

如果不勾选精确值,则统计的当前写入和待读出的数据为估计值,可能会相差2个左右。且fifo设计的wr_data_count.

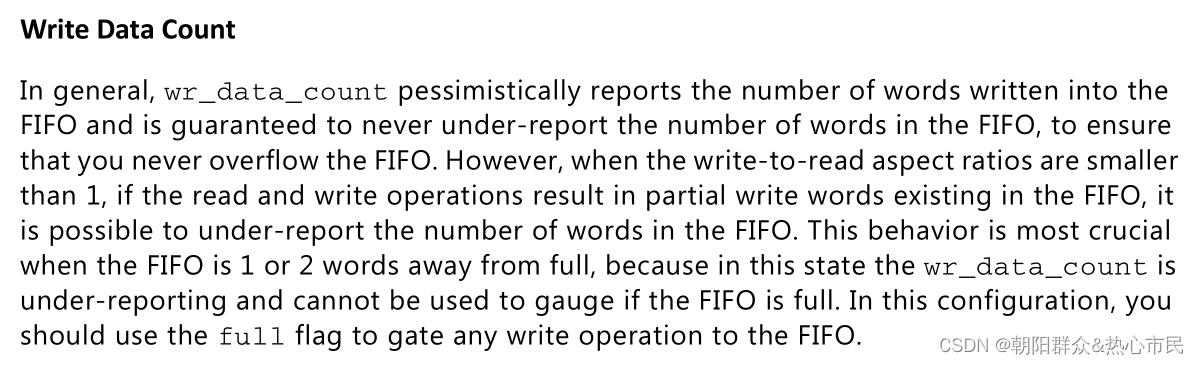

wr_data_count:当前的fifo中剩余已经写入的数据。

rd_data_count:当前的fifo中剩余可以读出的数据。

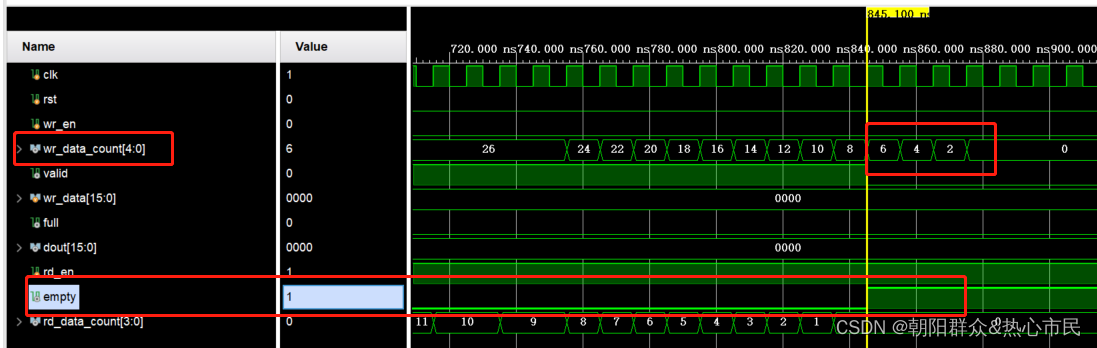

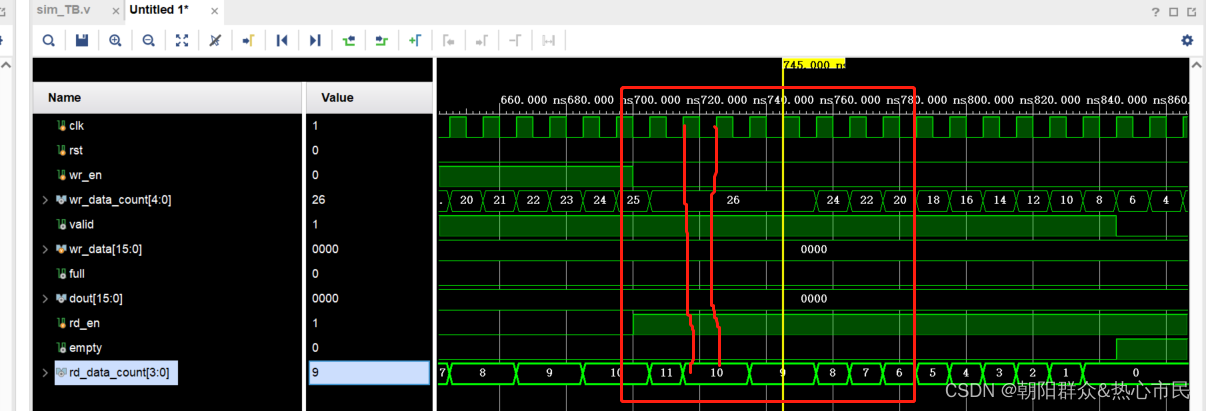

写数据个数保证不大于当前fifo中已有的个数,实际测试发现,当只写数据时,个数准确,如果同时读数据后,显示empty已经拉高,但wr_data_count仍不是0

如果需要判断fifo中的数值大于某个值后再进行读取,则只需要 rd_data_count即可。而且rd_data_count并不一定是读出一个数,相应的会变化一次,有可能会连个时钟周期变化一次

1695

1695

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?