前言

- 在行为级设计中,设计者需要在程序的多个不同地方实现同样的功能,这意味着有必要把这些公共的部分提取出来,将其组成子程序,在需要的地方调用这些子程序,以免重复编码。

- Verilog提供的任务和函数可以将较大的行为级计划分为较小的代码段,设计者将在多个地方使用的相同代码提取出来,编写成任务和函数,使得代码简洁、易懂。

- 任务与函数和命名块一样,也包含在设计层次中,可以通过层次名进行访问。

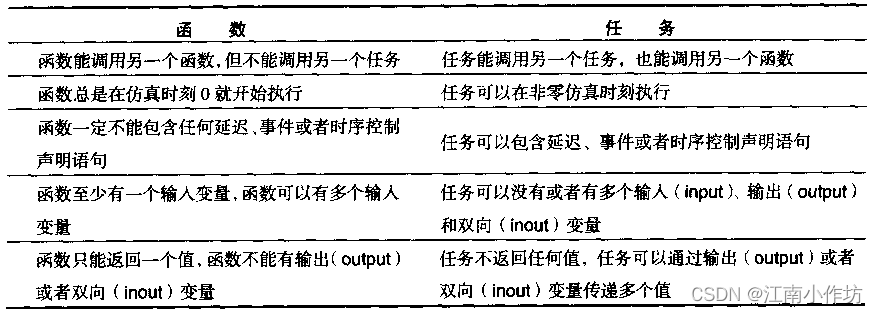

任务和函数的区别

- 任务和函数的目的不同。

- 如下表

- 任务和函数都必须在模块内进行定义,其作用范围仅局限于定义它们的模块。

- 任务用于代替普通的Verilog代码,其中可以包括延迟、时序、事件等语法结构,可以具有多个输出变量。

- 函数用于代替纯组合逻辑的Verilog代码,在仿真0时刻开始执行,只能有一个输出。

- 可以在任务和函数中声明局部变量,如寄存器、时间、整数、实数和事件,但是不能声明线网类型的变量。

- 任务和函数中只能使用行为级语句,但是不能包括

initial和always块。

任务

基本概念

-

关键字:

task...endtask -

子程序满足如下任一条件,则必须使用任务而不能用函数:

- 子程序中包含延迟、时序或事件控制结构;

- 没有输出或输出变量数目大于1;

- 没有输入变量;

-

任务的定义

task <任务名>; <端口及数据类型声明语句> <语句1> ... <语句n> endtask -

任务中的端口声明:input 输入、output输出、inout输出/输出,类似模块中声明端口,但是本质上有区别。模块的端口用来和外部信号相连接,任务的I/O变量则用来向任务中传入或从任务中传出变量。

-

举例,如对两个16位数进行按位与,按位或,按位异或。

//模块中启动任务 bitwise_oper(AB_AND, AB_OR, AB_XOR, A, B); //定义任务 task bitwise_oper

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1550

1550

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?