-

CDR的作用及应用场景

CDR的主要有两大作用,第一是为接收器端各电路提供时钟信号;第二是对接收到的信号进行判决,便于数据信号的恢复与后续处理。

-

CDR在各种高速PHY RX的应用:

比如高速phy(MIPI CPHY/ethernet phy)的RX端,这种情况下由于物理层信道中没有直接传输clk信号,所以需要从接收数据中恢复时钟频率和相位。

-

CDR在光信号上的应用

因为光信号传输至一定距离的时候,通常是长距离传输,其波形会出现一定程度的失真,接收端接收到的信号是一个个长短不一的脉冲信号,这个时候在接收端,我们就无法得到我们需要的数据。所以,这个时候就需要有信号的再生,信号的再生功能为再放大、再整形和再定时,其中的再定时指的就是CDR时钟数据恢复。总之,光模块中CDR时钟数据恢复功能的最大作用就是让接收端的信号与发射端信号保持一致。一般会使用到CDR的光模块,多数都是一些高速率、长距离传输的光模块,例如:10G SFP+ ER/10G SFP+ ZR一般都会用到的,使用CDR芯片的光模块会被锁定速率,不可以降频使用。

-

锁相环和倍频器

想要完成CDR少不了锁相环PLL(Phase Locked Loop)

2.1 倍频器实现原理

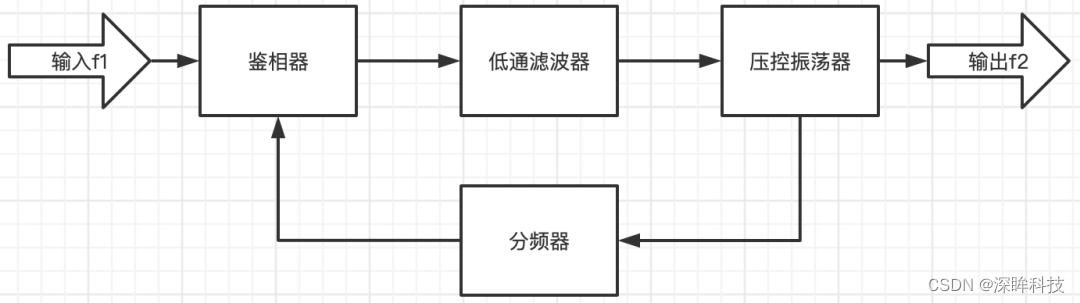

倍频器是利用了锁相环(Phase Locked Loop)负反馈控制系统实现的,锁相环简称PLL,PLL逻辑原理图如下所示:

① 输入F1

输入低频频率信号。

② 输出F2

输出倍频频率信号,为输入F1信号的N倍频。

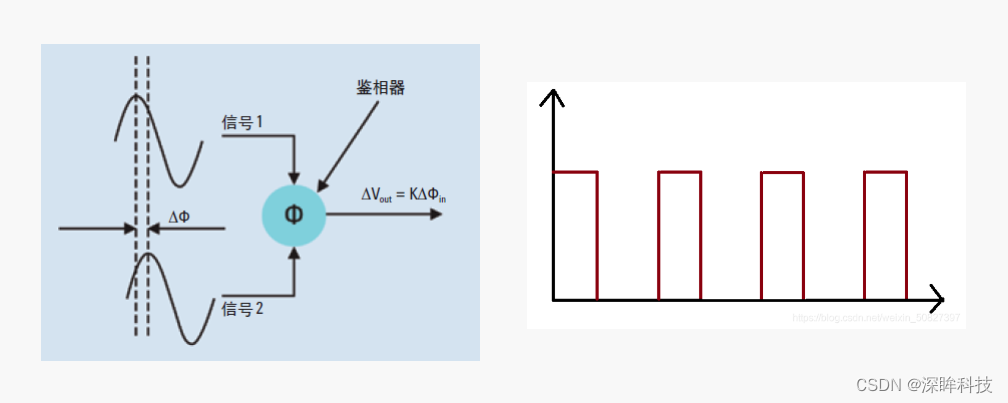

③ 鉴相器PD

使输出电压与两个输入信号之间的相位差有确定关系的电路,表示其间关系的函数称为鉴相特性,输出信号为矩形波,如下右图所示。

④ 分频器FD

使输出F2信号除N倍频输出,供给鉴相器,做负反馈,使电路构成自动调整相位差回路,电路稳定后F2 = N * F1。

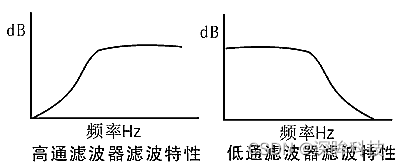

⑤ 低通滤波器LF

为了使信号变得平滑,如下图右侧所示,PD输出电路信号为矩形脉冲信号,所以需要采用低通滤波器使PD信号变得平滑。

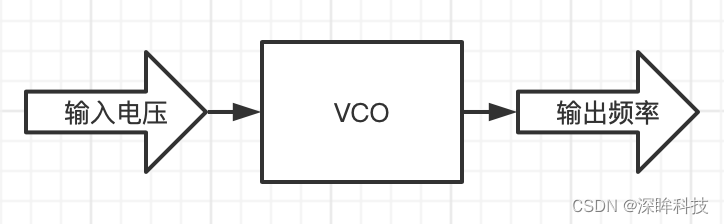

⑥ 压控振荡器VCO

Voltage Controlled Oscillator,为输入信号为电压,输出信号为频率的特殊电路,输出频率与输入电压成正比。

原文链接:深眸分享——一文看懂倍频器的原理及其应用_倍频电路_深眸科技的博客-CSDN博客

2.2 鉴相器

2.2.1 鉴相器的原理

可以参考以下专题

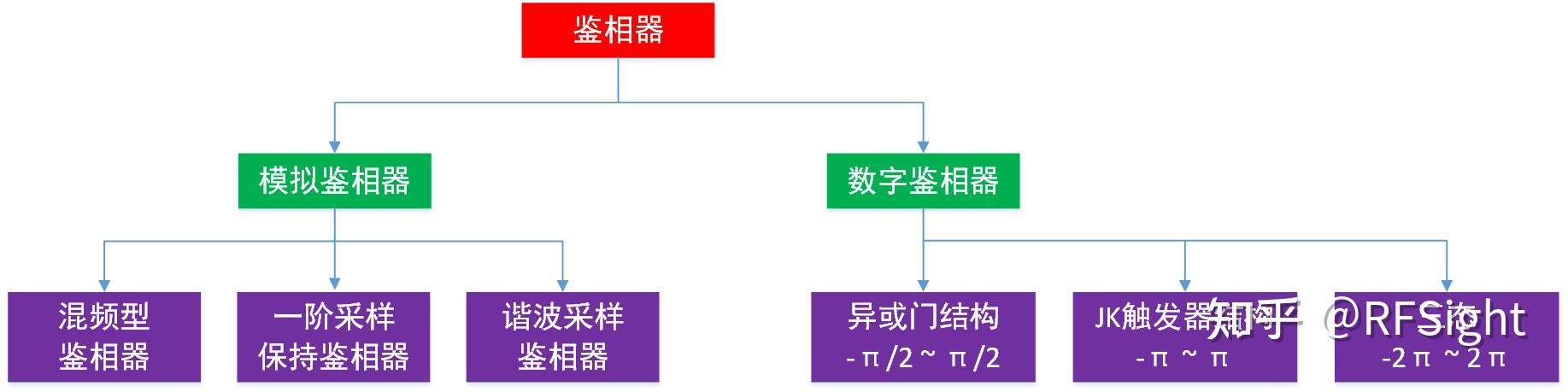

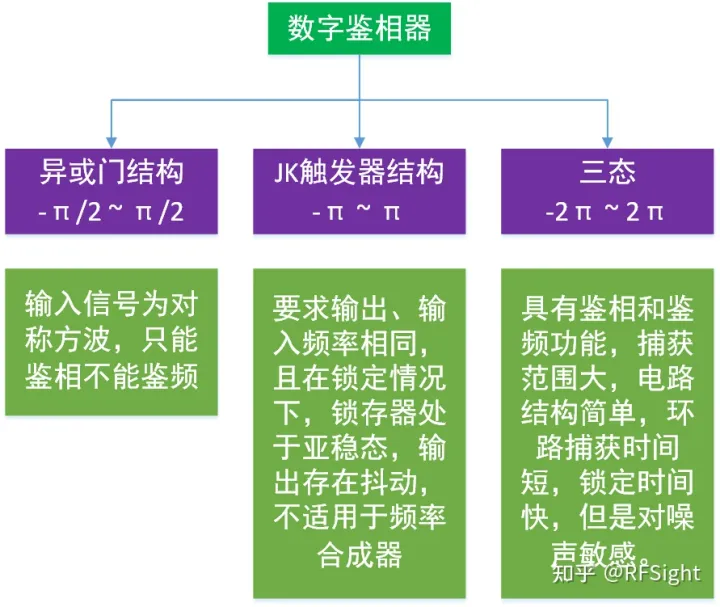

2.2.2 鉴相器的分类

以下分类摘自知乎

-

CDR的原理

CDR的具体实现方式有很多种,可以用模拟鉴相器做模拟反馈回路,也可以用数字鉴相器配合逻辑电路在数字域做反馈;可以用VCO来产生追踪输入频率的本地时钟,也可以用相位插值器来不断补偿相位误差。

分别参考以下两篇文章:

或者对应的本人转载的链接如下:

SerDes interface参考设计_CDR设计(5)_cdr原理_cy413026的博客-CSDN博客

时钟和数据恢复(CDR)电路原理——基于PLL_时钟数据恢复-CSDN博客

下面两篇文章详细补充了SerDes interface参考设计_CDR设计(5)文章中的相位插值法和过采样法

3.1 CDR与相位插值器

相位插值器需要多个不同相位的输入时钟,通常是四相输入或是八相输入,然后它会选取两个相邻的输入相位,对它们进行加权插值。通过调整两个相位的权重,相位插值器就可以输出任意相位的时钟。

其实相位插值算法 它的输入时钟频率和实际的采样频率并不需要相同,是直接进行相位反馈而不是频率反馈,就是通过不断调整采样点的相位值,来实现正确采样。

也可以用如下的方法理解:

存储正弦波的100个均分相位的波形值,然后用不同的速率来周期传输这100个值,那么产生的离散正弦波频率是和bit率相关的。

类比的由于在CDR中为了消除频率偏差,相位插值器通常都是在以一定速率不断地移动输出相位,它的输出就像在单位圆上不断旋转一样,这个不同的旋转速度就决定了输出的时钟频率。

RAMBUS就使用了相位插值作为CDR电路

本文介绍了CDR(ClockandDataRecovery)的作用,包括为接收端提供时钟信号和数据恢复,并探讨了其在高速PHYRX和光信号传输中的应用。CDR的实现涉及锁相环(PLL)、倍频器、鉴相器等组件。文中还提到了两种CDR实现方式:相位插值法和过采样法,以及相位插值器如何通过调整相位权重来实现正确采样。

本文介绍了CDR(ClockandDataRecovery)的作用,包括为接收端提供时钟信号和数据恢复,并探讨了其在高速PHYRX和光信号传输中的应用。CDR的实现涉及锁相环(PLL)、倍频器、鉴相器等组件。文中还提到了两种CDR实现方式:相位插值法和过采样法,以及相位插值器如何通过调整相位权重来实现正确采样。

2849

2849

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?