Design-for-Testability(DFT)的基本知识点

文章目录

基础知识

1. CP和FT

-

CP是(ChipProbe)的缩写,指的是芯片在wafer(晶圆)的阶段,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试,有时候这道工序也被称WS(WaferSort)

-

FT是Final Test的缩写,指的是芯片在封装完成以后进行的最终测试,只有通过测试的芯片才会被出货,详尽的测试。

参考https://blog.csdn.net/lzwsdu/article/details/53502894:

什么情况下需要CP?

-

因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的.而CP阶段则是可选

-

CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目.凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测.一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作.在FT阶段再确认具体的SNR/THD等指标

-

由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选.精细严格的测试放到FT阶段

-

如果封装成本不大,且芯片本身良率已经比较高.可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺

-

新的产品导入量产,应该先完成FT测试程序的开发核导入.在产品量产初期,FT远远比CP重要.等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试

2. 测试工程师需要考虑什么

降低测试成本:

- 从测试规划开始考虑芯片性能要求,ATE,Load Board等,通过减少chain length, memory instance number 来降低成本

- ATPG effciency

- 选择合适的test vectors

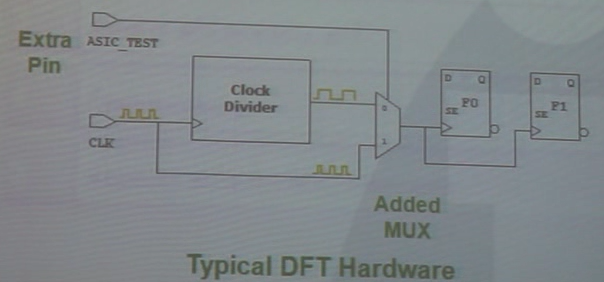

3. 什么是DFT

DFT = Design-for-Testability

-

额外的pin

-

会插入或改变原有的逻辑

DFT cost:

- area cost

- performance 降低

- ATPG tool cost 和 pattern debug cost

- ATE testing cost

如何减小DFT cost:

- 合理的test plan, 比如减小chain length, memory concurrent testing

- 减少图形(pattern) 数量

- 增加测试频率

Fault Model

physical fault:

- IO leakage 或 short

- net open

- material pollution

Logic fault:

- signal hard fault

- delay fault

- static current fault

Fault model 就是在physical fault 和 Logic fault之间建立一个桥梁,或者说是一个反应物理fault影响的逻辑模型

比如下面一个SA fault (static fault):

本文详细介绍了Design-for-Testability(DFT)的概念及其在集成电路测试中的应用,包括CP和FT测试的区别,测试工程师如何优化测试计划以降低成本,以及DFT方法如Scan、BIST、Boundary Scan的具体实现。

本文详细介绍了Design-for-Testability(DFT)的概念及其在集成电路测试中的应用,包括CP和FT测试的区别,测试工程师如何优化测试计划以降低成本,以及DFT方法如Scan、BIST、Boundary Scan的具体实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2565

2565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?