在实际的项目中,我们经常会碰到需要约束时钟独立的情况,今天就来学习一下exclusive时钟如何约束的概念。

1:如果两个时钟C1和C2是logically exclusive的,这意味着这两个时钟共存于设计中,但是彼此之间没有任何交流,“共存在设计中”的意思是某一时刻这两个时钟信号都是存在的;彼此之间没有任何交流的意思是:不存在任何时序路径,其起点是由C1驱动的,而终点是由C2驱动的,也不存在任何路径,其起点是由C2驱动,而其终点是由C1驱动的。

上图所示C1和C2是典型的logically exclusive,他们共存于设计中,而且时钟信号同时都有,但他们没有任何交互。

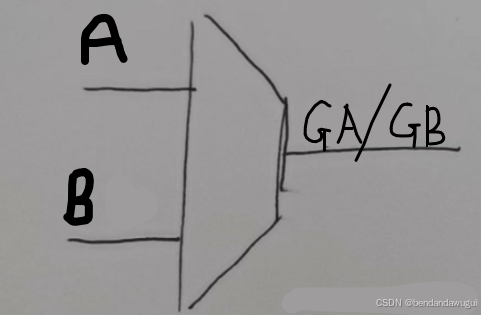

2:如果两个时钟A和B是physically exclusive的,那说明这两个时钟信号是不能共存于整个设计中的,最典型的例子就是两个时钟信号通过一个MUX输出。

如图,MUX的输出Z可能会是A的时钟信号,也可能是B的时钟信号,但是无论如何,Z端的输出不可能同时是A和B,因此在Z端所定义的两个生成时钟GA和GB是physically exclusive的。

3:asynchronous

如果两个时钟是异步的,那么就定义为asynchronous,“异步”是指时钟之间没有固定的相位关系。

但是他们都有一个共同点,这三个约束都会让时序分析工具停止对相关时序路径的分析,因此都会忽略掉相关的时序违例,仅仅从这个角度看,无论是logically还是physically还是asynchronous,效果是一样的。

下面给出几种典型电路以及正确的时钟定义。

a:对于logically exclusive的处理:

如果上图C1和C2是logically exclusive的,那么正确的约束命令如下:

create_clock -period 10 -name C1 [get_ports C1]

create_clock -period 20 -name C2 [get_ports C2]

set_clock_groups -logically_exclusive -group C1 -group C2

图中C1端口经过走线到达MUX的输入端口A,之所以要在A处定义生成时钟,是为了使约束命令向后兼容代码,如下图中所示,如果在后续版本中的代码中,C1和C2时钟的logically exclusive关系消失,而同时我们一开始就定义C1和C2是logically exlusive的,那么此时就会错误的省去某些path的时序分析从而埋下隐患。

b:physically exclusive

对于上图中所示的GC1和GC2,他们是physically exclusive的,对于GC1和GC2的正确处理如下:

create_clock -period 10 -name C1 [get_ports C1]

create_clock -period 20 -name C2 [get_ports C2]

create_generated_clock

-name muxGC1 \

get_pins mux1/Z \

-source [get_pins mux1/A] \

-combinational

create_generated_clock

-name muxGC2 \

get_pins mux1/Z \

-source [get_pins mux1/B] \

-combinational -add

set_clock_groups -physically_exclusive -group muxGC1 -group muxGC2

这里GC1和GC2由于其source object都是mux1/Z,即他们的物理位置是一样的,因此要在最后加入-add,否则后面的命令将覆盖前面的命令,导致只有GC2被定义,而-combination 的意思是生成时钟的源 -source所指定的位置到生成时钟的source object之间是纯组合逻辑(MUX1/A到MUX1/Z之间是纯组合逻辑)

所以 logical exclusive 与 physical exclusive 的区别就是:

如果两个 clock 同时存在,且有一个选择端控制这两个信号,那么它们就是 logical exclusive

如果两个 clock 不可能同时出现在电路中(比如定义在同一个点上),那么它们就是 physical exclusive。

在第二个图中,如果把 C1 C2 声明成 physical exclusive,会有什么问题?

虽然 logical exclusive 和 physical exclusive 都可以保证 C1 C2 之间不做 timing check,

但是 logical exclusive 情况下,工具会计算 C1 C2 之间的 crosstalk;

这里用一张图来说明一下这个crosstalk是啥:

图中对crossing(crosstalk)进行了标注, 就是红色的path,这里说了这个cross是non-exclusive的,clka是launch ,clkb是capture。工具检查的就是这个cross。只要约束了logic exclusive,那么就会报这个warning。

而在 physical exclusive 情况下,则不会计算 crosstalk。

在第二个图中,C1 C2 有各自单独的走线,它们之间的是有可能出现 crosstalk 的,所以不能声明成 physical exclusive。

教材解释:

文章介绍了在数字设计中,exclusive时钟约束的概念,包括logicallyexclusive(逻辑独立)和physicallyexclusive(物理独立)时钟,以及它们在时序分析中的作用。通过实例解释了如何对这类时钟进行正确的创建和约束,强调了正确约束的重要性,以避免时序违例并确保设计的正确性。

文章介绍了在数字设计中,exclusive时钟约束的概念,包括logicallyexclusive(逻辑独立)和physicallyexclusive(物理独立)时钟,以及它们在时序分析中的作用。通过实例解释了如何对这类时钟进行正确的创建和约束,强调了正确约束的重要性,以避免时序违例并确保设计的正确性。

378

378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?