概述

Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计。“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线。IP核一部分来自于Xilinx官方IP;一部分来自于第三方IP,其中有的是在网络上开源的;另一部分就是自己设计的IP。有时候我们需要把自己的一个设计反复用到以后的工程中,利用Vivado的“IP Package”将其封装起来,再以后的工程中直接调用即可。

本文致力于讲述如何将自己的设计封装为IP核,以及示范一下如何在其它工程中调用自己设计好的IP核。本文采用的设计是一个简单的位宽可设置的加法器。博主使用的Vivado版本是2017.1,其它版本在一些设置的地方可能存在一些差异。

封装IP

1. 首先建立一个工程用于设计IP核,这个工程最好放在Vivado目录下或不会被删除的地方。添加一个源文件,输入一个简单的组合逻辑加法器的代码:

`timescale 1ns / 1ps

module Add_USR_IP #(parameter WIDTH = 1)(

input [WIDTH:0] a,

input [WIDTH:0] b,

output cout,

output [WIDTH:0] c

);

assign {cout, c} = a + b;

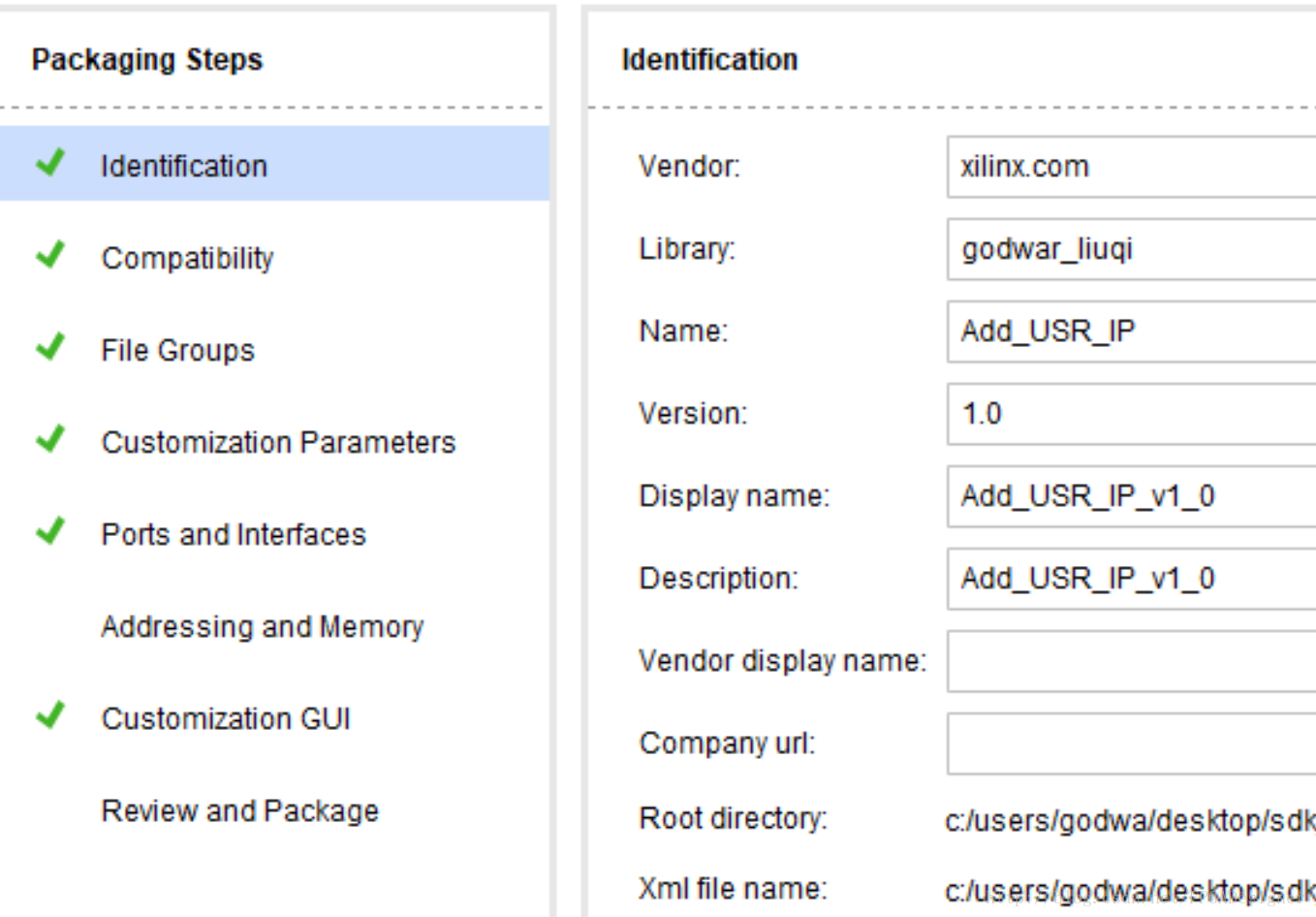

endmodule 2. 点击左边“Flow Navigator”中的“Settings”,打开“IP”下的“Packager”。设置自己的IP核的库名和目录,我将Library更改为了“godwar_liuqi”,Category更改为了“/godwar_liuqi_IPLib”。这里也可以用默认值。

3. 点击上方菜单栏中的“Tools”下的“Create and Package New IP”,跟着流程一直走最后Finish即可,将在工作区弹出如下界面,包含了IP核的一些信息,名称为“Add_USR_IP_v1_0”。

**4**. 在上述界面的“Compatibility”标签下给出了这个IP可以支持的FPGA系列,默认是支持全部系列。“File Groups”中可以看到这个IP包含的文件,可以为这个IP添加一个仿真文件来验证其功能。 **5**. 我为了实现加法位宽可调整,源程序中使用了parameter参数。打开上述界面中的“Customization Parameters”标签,将看到这个参数WIDTH:

**4**. 在上述界面的“Compatibility”标签下给出了这个IP可以支持的FPGA系列,默认是支持全部系列。“File Groups”中可以看到这个IP包含的文件,可以为这个IP添加一个仿真文件来验证其功能。 **5**. 我为了实现加法位宽可调整,源程序中使用了parameter参数。打开上述界面中的“Customization Parameters”标签,将看到这个参数WIDTH:

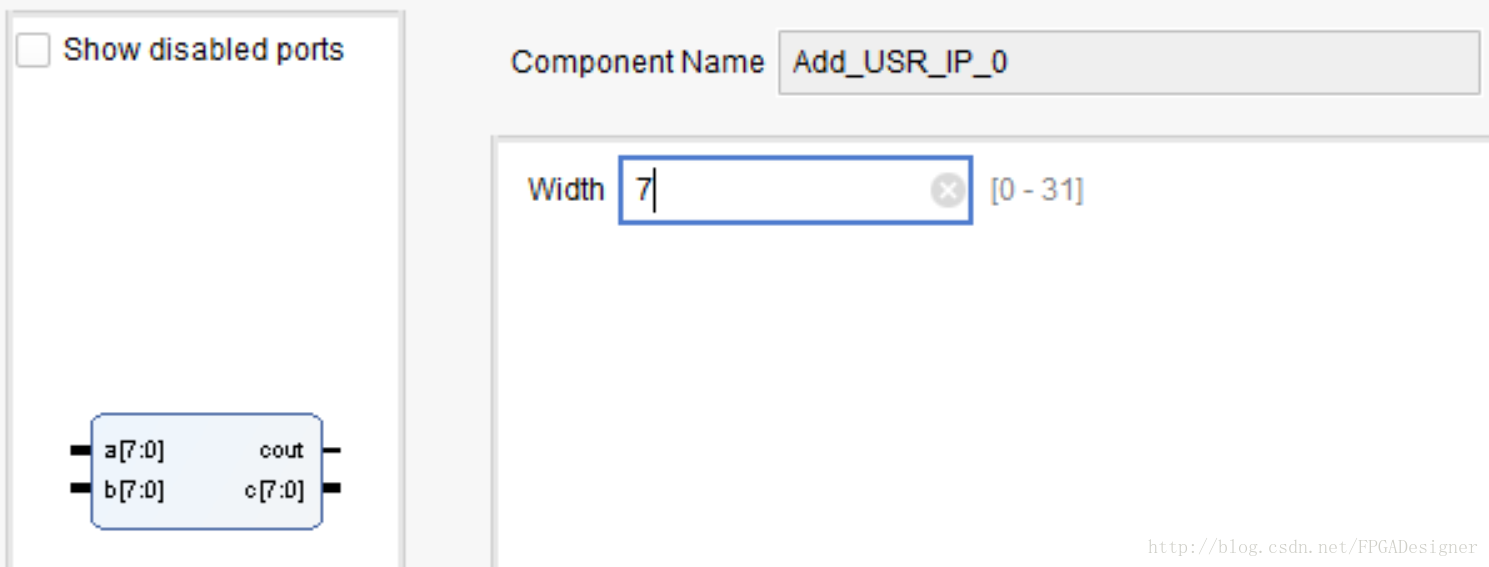

双击WIDTH,将弹出一个参数设置框。里面可以指定这个参数在配置IP核是的格式以及是否可以被用户编辑。我们在这里将“Specify Range”勾选中,将Type更改为“Range of integers”,表示此参数可以选择的范围。将Minimum设置为0,Maximum设置为31,表示该IP核最高可设置为32位的加法器。最后再将“Default Value”指定为7,表示默认为8位加法器。 **6**. 第3步骤的“Ports and Interfaces”中将看到IP核的管脚信息,“Customization GUI”中将看到IP核的原理图图形。没有问题后切换到“Review and Package”标签,点击“Package IP”会提示成功生成IP核。 ———-

双击WIDTH,将弹出一个参数设置框。里面可以指定这个参数在配置IP核是的格式以及是否可以被用户编辑。我们在这里将“Specify Range”勾选中,将Type更改为“Range of integers”,表示此参数可以选择的范围。将Minimum设置为0,Maximum设置为31,表示该IP核最高可设置为32位的加法器。最后再将“Default Value”指定为7,表示默认为8位加法器。 **6**. 第3步骤的“Ports and Interfaces”中将看到IP核的管脚信息,“Customization GUI”中将看到IP核的原理图图形。没有问题后切换到“Review and Package”标签,点击“Package IP”会提示成功生成IP核。 ———-

调用自己的IP核

再另外新建一个工程,我们尝试调用刚才自己制作的IP核。建立好工程后先不添加源文件。在“Flow Navigator”的“Settings”中选中“IP”下的“Repository”,点击“+”添加,路径指定到刚才封装IP核的目录。点击ok后便会弹出一个框提示找到了一个名为“Add_USR_IP_v1_0”的IP核,也就是刚才创建的加法器。

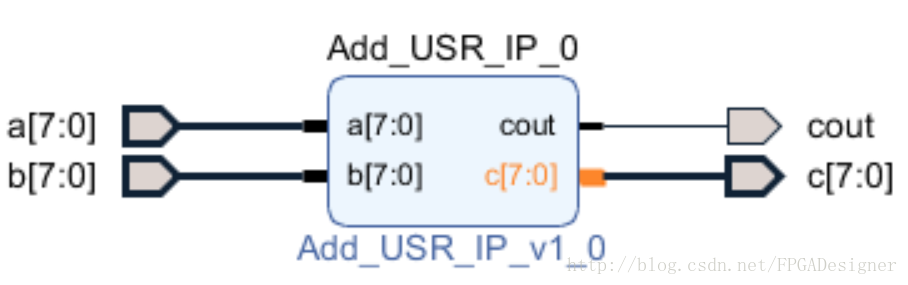

设置好后在“IP Integrator”中点击“Create Block Design”,创建一张原理图。原理图中点击“+”搜索Add_USR_IP_v1_0,即可看到自己制作的IP核,双击添加到原理图中。如果设计中还需要其它IP核,添加IP后用连线连接起整个系统即可。双击IP核图形,即可弹出配置界面,可以更改加法器的位宽。

这里我们不使用其它IP,直接在Add_USR_IP_v1_0的管脚上右键,点击“Make External”生成管脚信号。结果如下:

在“Design Sources”中我们将看到bd后缀的原理图文件。为了使用方便,保存原理图后我们在文件上点右键,点击“Create HDL Wrapper”,软件会将原理图封装为一个Verilog文件,这个Verilog文件可以供其它模块调用。结果如下所示:

设计好后可以像普通的工程一样综合、实现、生成bit流。值得一提的是,在这个工程中我们是无法查看到Add_USR_IP_v1_0这个IP核的源码的,它是一个黑盒的状态。这也是Vivado提供的IP加密技术,以保护设计者的权益。

4424

4424

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?