全加器是指对输入的两个二进制数相加(A与B)同时会输入一个低位传来的进位,得到和数(SUM)和进位

;一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

真值表

| A | B | SUM | ||

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

真值表达式

verilog代码

`timescale 1ns / 1ps

module add(

input A,

input B,

input Ci1,

output SUM,

output Ci

);

assign SUM = A ^ B ^ Ci1;

assign Ci = (A & Ci1) | (A & B) | (B & Ci1);

endmoduletestbench

`timescale 1ns / 1ps

module add_tb(

);

reg A;

reg B;

reg Ci1;

wire SUM;

wire Ci;

add add1(

.A(A),

.B(B),

.Ci1(Ci1),

.SUM(SUM),

.Ci(Ci)

);

initial begin

A = 1;

B = 1;

Ci1 = 1;

#10

$display("A = %d, B = %d, Ci1 = %d, SUM = %d, Ci = %d",A,B,Ci1,SUM,Ci);

A = 0;

B = 1;

Ci1 = 1;

#10

$display("A = %d, B = %d, Ci1 = %d, SUM = %d, Ci = %d",A,B,Ci1,SUM,Ci);

$finish;

end

endmodule

仿真结果

RTL实现

可以看到RTL实现与真值表达式实现结构相同。

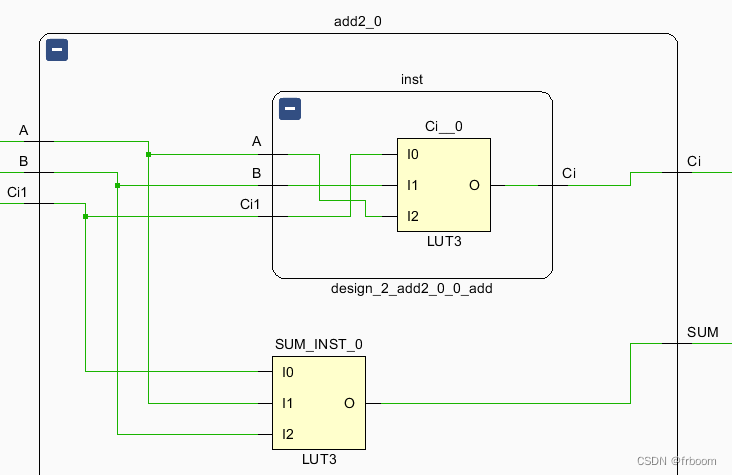

综合结果为

全加器由两个3输入1输出的查找表实现

实现结果为

最终在7K325T上一个全加器由一个6输入2输出的查找表实现,所以我们可以得知一个6输入2输出的查找表刚刚好可以实现一个全加器。

还有另一种真值表达式

verilog 代码

`timescale 1ns / 1ps

module add(

input A,

input B,

input Ci1,

output SUM,

output Ci

);

assign SUM = A ^ B ^ Ci1;

assign Ci = ((A ^ B) & Ci1) | (A & B);

endmoduleRTL实现

综合

使用两个3输入1输出的查找表实现。

实现

可以看到全加器最终被实现为7K325T上的两个查找表了,资源消耗多一些并不代表设计就差,本实验只是单纯总实现与资源的角度进行分析,但是没有考虑时延,后续会单独针对时延进行分析,综合资源与时延进行分析。

1076

1076

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?