CMOS芯片损坏导致主板无法保存BIOS设置?BIOS固件升级失败引发系统崩溃?

一、CMOS与BIOS基础定义

1. CMOS技术本质

CMOS(互补金属氧化物半导体)是一种集成电路工艺,用于制造低功耗数字电路。计算机主板的CMOS芯片是特殊RAM,存储BIOS配置参数(时间、启动顺序等),依赖纽扣电池供电保持数据。

2. BIOS功能定位

BIOS(基本输入输出系统)是固化在ROM芯片上的程序,负责开机自检、硬件初始化和启动引导。最新UEFI BIOS支持图形界面和鼠标操作,但核心功能不变。

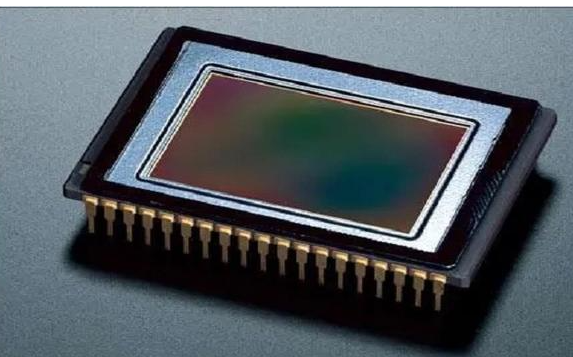

3. 物理形态对比

CM芯片:通常为DIP8或SOP8封装的RAM(如ST M48T86)

BIOS芯片:多采用PLCC32或SOIC8封装的Flash ROM(如Winbond W25Q128)

二、硬件设计中的交互关系

1. 数据存储机制

BIOS程序写入CMOS芯片的典型流程:

用户进入BIOS界面修改参数

BIOS将新配置写入CMOS RAM(地址0x70/0x71)

关机后CR2032电池维持CMOS数据

2. 功耗特性对比

CMOS静态电流:≤1μA(3V供电时)

BIOS读写电流:15mA(编程状态)

3. 信号接口差异

CMOS芯片:I2C或SPI接口(频率400kHz1MHz)

BIOS芯片:LPC或eSPI接口(速度33MHz66MHz)

三、典型故障排查方法

1. CMOS常见问题

数据丢失:纽扣电池电压<2.5V时发生,更换电池并重设参数

配置错误:Clear CMOS跳线短接5秒恢复出厂设置

物理损坏:ESD击穿芯片,需更换并检查PCB接地

2. BIOS故障处理

启动失败:使用编程器重刷BIOS文件(如.fd格式)

兼容问题:更新微码(Microcode)修复CPU漏洞

校验错误:检查Flash ROM的WP引脚电平状态

四、PCB设计关键要点

1. CMOS电路布局规范

电池供电线路线宽≥0.3mm,远离高频信号

CMOS芯片与MCU间距≤5cm,减少I2C信号衰减

2. BIOS电路防护设计

Flash ROM的VCC引脚并联10μF+0.1μF电容

地址线长度差控制在±50mil内

使用TVS管防护编程接口(如SMAJ5.0A)

3. EMC设计注意事项

BIOS时钟线包地处理,两侧布设地线

CMOS电池走线套磁环(100MHz阻抗≥600Ω)

五、技术演进趋势

1. CMOS工艺升级

40nm以下工艺的CMOS芯片漏电流降低至pA级

新型FRAM(铁电存储器)逐步替代传统CMOS RAM

2. BIOS架构变革

UEFI取代传统Legacy BIOS,支持GPT分区和Secure Boot

开源Coreboot项目可定制BIOS功能模块

3. 集成化设计

部分SoC将CMOS与RTC集成(如STM32MP157)

eSPI接口替代LPC,传输速率提升4倍

CMOS与BIOS的协同设计直接影响系统可靠性。建议在PCB投板前做BIOS刷写测试,并验证CMOS数据保持时间。

335

335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?