目录

一、概述

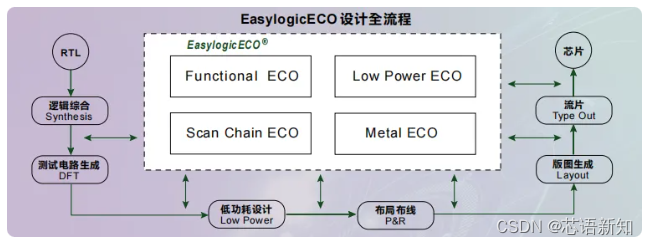

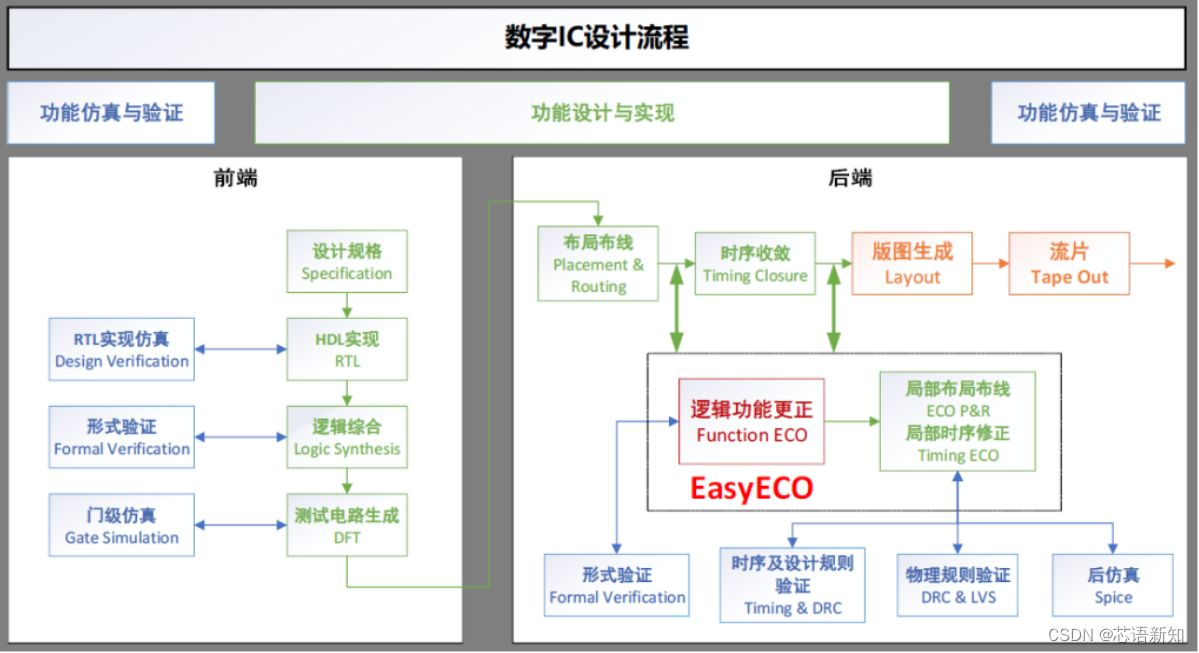

在IC设计的整个流程,对于IC设计工程师来说,有一个关键的节点,叫做RTL freeze ,在此之后基本是不允许修改RTL代码的,因为一动RTL就需要重新综合,影响IC后端的schedule和整体项目进展,此时修改BUG用到的方法叫做ECO。IC设计流程中的ECO(Engineering Change Order,工程变更指令)可以在多个阶段进行,但主要分为两大类:Pre-Mask ECO和Post-Mask ECO,它们对应不同的实施阶段和成本消耗。

Pre-Mask ECO

- 阶段:这一阶段的ECO发生在设计的前端到后端流程之间,特别是在布局布线(Place and Route, P&R)之后但在制造掩模之前。此时,设计团队可以对逻辑、电路结构、布局或早期的金属层进行修改。

- 成本:由于修改发生在物理实现的较早阶段,尽管可能需要重新进行逻辑综合、布局和布线,但相比Post-Mask ECO,成本相对较低。主要是时间成本和计算资源消耗,因为无需制作新的掩模。

Post-Mask ECO

- 阶段:当设计已经完成并制造了光刻掩模后,如果发现需要修改,就只能进行Post-Mask ECO。这种情况下,修改通常局限于金属层(Metal ECO),以避免重新制造掩模的巨大成本。

- 成本:Post-Mask ECO的成本较高,因为它涉及到对已有的物理设计进行局部调整,这可能需要手工或自动的金属层重新路由,以及额外的验证工作。虽然避免了掩模重制费用,但是ECO实施的复杂性和验证成本,以及可能对生产计划的延迟,都会显著增加总体成本。

- Metal ECO特别指出,它专注于通过修改顶层金属互连线来解决时序问题或小的功能调整,这通常需要专用的ECO工具来执行并确保修改不影响其他设计特性。

总结

ECO的实施阶段越晚,对项目时间和成本的影响越大。Pre-Mask ECO虽然灵活度高,但应尽量减少以控制项目进度和成本。Post-Mask ECO,特别是Metal ECO,是成本敏感的,应当谨慎评估变更的必要性和潜在影响,确保只有在必要且经济效益合理的情况下才进行。在整个设计流程中,有效的ECO管理策略对于控制成本和保证产品质量至关重要。

二、Pre-Mask ECO(预掩模ECO)

Pre-Mask ECO,全称为Pre-Mask Engineering Change Order,是指在集成电路(IC)设计流程中,在制造光刻掩模之前的工程变更指令。这一阶段的ECO具有高度的灵活性,允许设计团队对设计的各个方面进行较为广泛的修改,而不受掩模制作完成后修改难度和成本激增的限制。下面是Pre-Mask ECO的详细介绍:

实施阶段

Pre-Mask ECO通常在以下设计阶段实施:

- 逻辑综合后:发现逻辑错误或需要优化逻辑实现时。

- 布局过程中:为了改善电路的布局,比如优化面积利用率、改进电源分配或解决布局冲突。

- 布线前后:在完成初步布线后,通过静态时序分析(STA)发现时序违规或者需要改进信号完整性时。

- 签核(Sign-off)前:在设计正式签署用于制造之前,对设计进行全面检查并修正发现的问题。

修改内容

在Pre-Mask阶段,可以进行的修改包括但不限于:

- 逻辑更改:增加、删除或修改逻辑门、状态机或其他逻辑模块。

- 布局调整:移动或重新安排标准单元、宏单元的位置,以优化布局。

- 布线重做:调整或重新布线信号路径,解决时序或电气问题。

- 功耗优化:通过修改设计来减少动态功耗或泄漏功耗。

- 面积优化:减小芯片的总面积,提升生产经济性。

工具与流程

实施Pre-Mask ECO通常涉及以下工具和流程:

- 逻辑综合工具(如Synopsys Design Compiler、Cadence Genus):用于重新生成逻辑网表。

- 布局与布线工具(如Cadence Innovus、Synopsys IC Compiler):用于调整布局和重新布线。

- 静态时序分析(STA)工具:确保设计满足时序要求。

- 形式验证工具(Formal Verification):确认设计变更前后功能的一致性。

- 物理验证工具:执行设计规则检查(DRC)、布局与原理图比较(LVS)等,确保设计的物理实现正确无误。

成本与风险

尽管Pre-Mask ECO提供了较大的修改自由度,但每次ECO操作都需要重新进行验证和签核流程,可能会延长设计周期。然而,相比于Post-Mask ECO,它仍然被认为是成本效益较高的,因为没有涉及到掩模层的物理改变,因此不需要承担重新制造掩模的高额费用。

总结

Pre-Mask ECO是IC设计流程中一个至关重要的环节,它允许设计团队在制造前对设计进行必要的优化和修正,以确保最终产品的质量和可靠性。通过高效的ECO管理,可以有效平衡设计性能、成本和上市时间之间的关系。

三、Post-Mask ECO(后掩模ECO)

Post-Mask ECO,全称为Post-Mask Engineering Change Order,是在集成电路(IC)设计的后期阶段,即光刻掩模已经制作完成,但尚未进行最终的金属层连线加工时所进行的工程变更指令。这一阶段的ECO由于受到物理实现的限制,只能进行相对有限且不涉及基础层更改的修改。以下是Post-Mask ECO的详细介绍:

实施背景

- 后期发现的问题:在设计验证的最后阶段,如后硅验证或原型测试中,可能发现时序问题、功能错误或需要的小幅性能调整。

- 成本与时间考量:虽然发现问题,但考虑到重新制作全部掩模的成本高昂且耗时,因此选择只修改金属层。

修改限制

- 金属层改动:仅限于修改上层金属连线,不涉及晶体管或低层互连的改变。

- 备用单元(Spare Cells)利用:利用预先在设计中预留的Spare Cells进行逻辑修改。这些单元可以在不改变底层布局的情况下,通过金属层连线的变动来实现新的逻辑功能。

- Freed Cells:已分配但未使用的逻辑单元也可以被重新分配新的逻辑功能。

- GA Cells(Generic Array Cells):通用数组单元,可以编程为不同功能,用于实现小范围的逻辑变化。

实施流程

- 问题识别与分析:确定需要修改的具体问题,并评估是否可以通过Post-Mask ECO解决。

- ECO规划:基于现有设计和Spare Cells的位置,规划最小影响的修改方案。

- ECO实施:使用EDA工具(如Cadence Virtuoso或Synopsys ICC)对金属层进行修改,同时确保修改不会影响原有的设计功能和DFT(Design-for-Test)结构。

- 验证与签核:进行时序分析、DRC(Design Rule Check)、LVS(Layout Versus Schematic)和电气规则检查,确保修改后的设计仍符合规范。

- 形式验证:利用形式验证工具确保修改前后逻辑功能的一致性。

- ECO实施审核:团队审核ECO变更,确保变更的合理性和必要性。

风险与挑战

- 局限性:由于只能修改金属层,对设计的改动非常有限。

- 复杂性:确保修改不影响其他功能或导致时序问题,增加了设计的复杂性。

- 资源依赖:依赖于设计中预置的Spare Cells,若数量不足或位置不佳,可能无法实施所需的修改。

- 验证难度:确保修改正确无误需要全面而严格的验证流程,这可能会延迟产品上市时间。

总结

Post-Mask ECO是IC设计后期的一种补救措施,旨在通过最小的物理改动解决发现的问题。它要求精确且谨慎的操作,以避免引入新的问题,同时要高效快速以减少对项目进度的影响。虽然受限较多,但在某些情况下,它是避免高昂的重新制造掩模成本的最佳选择。

四、Metal ECO(金属层工程变更指令)

Metal ECO(金属层工程变更指令)是Post-Mask ECO(后掩模工程变更指令)的一个具体类型,专注于在集成电路(IC)设计流程的后期,当光刻掩模已经制作完毕后,仅对金属互连层进行的修改。这一阶段的修改极为关键,因为它需要在不改变底层晶体管结构的前提下,通过调整或重做金属连线来修复时序问题、纠正设计错误或满足新的设计要求。以下是Metal ECO的详细说明:

实施目的

- 时序收敛:解决在后期验证中发现的时序违规问题,如建立时间(setup time)或保持时间(hold time)不满足要求。

- 功能修正:修正因设计疏漏或验证遗漏导致的功能错误,而这些错误通过金属层的微调即可解决。

- 性能优化:轻微调整以提高信号完整性、减少串扰或优化功耗。

修改范围

- 金属层重路由:重新布局金属连线路径,以避开拥挤区域或缩短关键路径长度。

- 插入缓冲器/终端电阻:在关键路径上添加缓冲器来调整延时,或在信号线上加入终端电阻以改善信号质量。

- 电源/地网格调整:优化金属层的电源和地线分布,改善电源完整性。

- 利用备用金属层:如果设计中包含备用金属层或未充分利用的金属资源,这些资源可以被重新分配以实现必要的修改。

实施工具与流程

- ECO工具:使用专业的ECO工具,如Synopsys’ IC Compiler 或 Cadence’s Innovus,这些工具支持在现有布局上进行金属层的改动,并提供即时的时序反馈和DRC检查。

- 时序分析:执行静态时序分析(STA)来验证修改后的设计是否满足所有时序约束。

- 物理验证:进行设计规则检查(DRC)和布局与原理图一致性检查(LVS),确保修改没有违反制造规则,且逻辑功能保持不变。

- 形式等价性检查(LEC):在某些情况下,执行LEC以验证修改前后设计的逻辑功能保持一致。

挑战与风险

- 时序收敛风险:金属层的改动可能会影响到其他原本满足时序的路径,导致连锁反应。

- 面积和功耗影响:额外的缓冲器或更复杂的连线路径可能增加芯片的面积和功耗。

- 验证难度:确保在有限的修改范围内不会引入新的问题,需要详尽的验证工作。

成本与效益

Metal ECO相比重新制作掩模的全量修改成本要低得多,但依然需要投入大量的工程时间和资源。因此,其成本效益在于能够在不显著推迟项目进度和增加成本的前提下,快速响应设计上的紧急需求。正确的决策和高效的实施流程对于成功执行Metal ECO至关重要。

五、实施策略与注意事项

- 最小化影响:无论是哪种ECO,目标都是在解决问题的同时,尽可能减少对现有设计的其他方面造成的影响。

- 验证:每次ECO后都需要进行全面的验证,包括功能验证(LEC)、时序验证、DRC/LVS(Layout Versus Schematic)检查等,确保修改正确无误。

- 成本考量:Post-Mask ECO尤其是Metal ECO虽然成本低于全面重做掩模,但仍需考虑其对项目时间和预算的影响。

综上所述,IC设计中的ECO管理是确保设计质量、按时交付的关键环节,选择合适的工具和策略对于高效完成ECO至关重要。

感谢阅读!!

929

929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?