1,如何保持信号不被综合

对这种情况的处理是增加约束,共有2种情况:

a, 需要保留的信号类型是 wire

在定义的时候在后面增加/* synthesis keep */。

例如:wire wire_name/*synthesis keep */;

b,需要保留的信号类型是 reg

跟reg相关的synthesis attribute,共有两种,分别是/*synthesis noprune*/和/*synthesis preserve*/,两者的差别如下:

/*synthesis noprune*/ 避免 Quartus II 优化掉没output的reg。

/*synthesis preserve*/避免 Quartus II 將reg优化为常数,或者合并重复的reg。

定义的时候在后面增加相关的约束语句。

例如:reg r_name/*synthesis noprune*/; 或者 reg r_name/*synthesis preserve */;

將/*synthesis noprune*/等synthesis attribute 语句放在module后面,这样整个module的所有reg将不被优化,

从而不用再一一寄存器指定。

注意:以上所提到的使用语言为verilog。synthesis attribute必须写在结束分号前面, 写在分号后面只相当于注释:

正确:reg r_name/* synthesis preserve */;

错误:reg r_name;/* synthesis preserve */

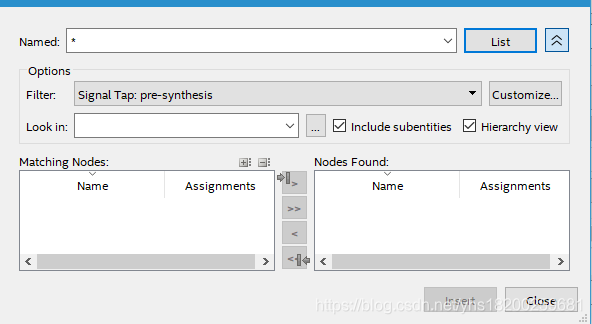

2,如何快速找到想要抓取的信号

选择 filter 为 Signal Tap : pre-synthesis 。对于模块间的信号,Named 填入模块的端口名,注意不要填模块间的网络名,

对于模块内部的信号, 可以直接搜索,如果找不到, 可以参考1增加相应约束。

474

474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?