【JESD79-5之】14 DDR5模块Rank和Channel的时序

14.1 DDR5 DIMMs模块rank和channel的限制

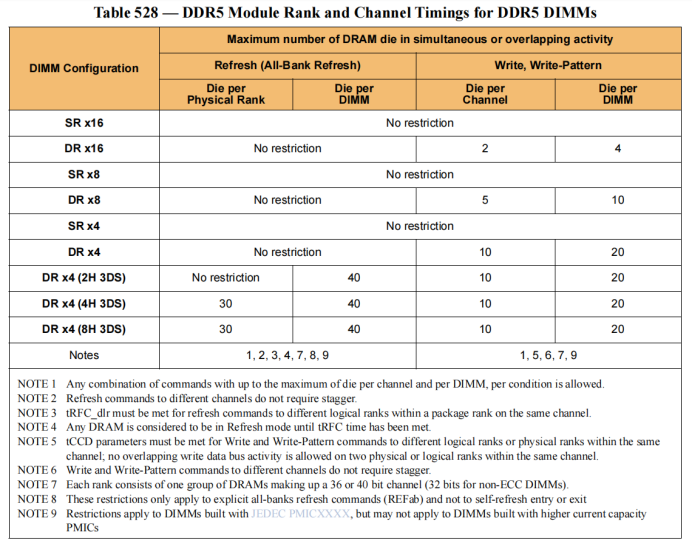

为了实现JEDEC标准DDR5 DIMMs的高效模块电源设计,单个模块上发生的Refresh和Write命令操作有最小时序和DRAMs数量的限制。此外,由于这些模块被组织为两个独立的36位或40位通道(无ECC的DIMMs为32位),因此应用了额外的限制,以限制模块上的局部电源传输噪声。

为了提供最好的性能,不同的通道可以在同一周期中发起命令,前提是在这个周期内满足rank到rank的时序,给定激活命令中的最大DRAMs数量不超,并且满足本规范中其他地方所示的适用组件时序。DDR5 DIMMs的时序和操作关系如表528所示。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?