- type 1与 type 2之间的差距

- 实际设计方面的问题

- CPPLL瞬态响应

- 数字锁相环的数字滤波器基本结构

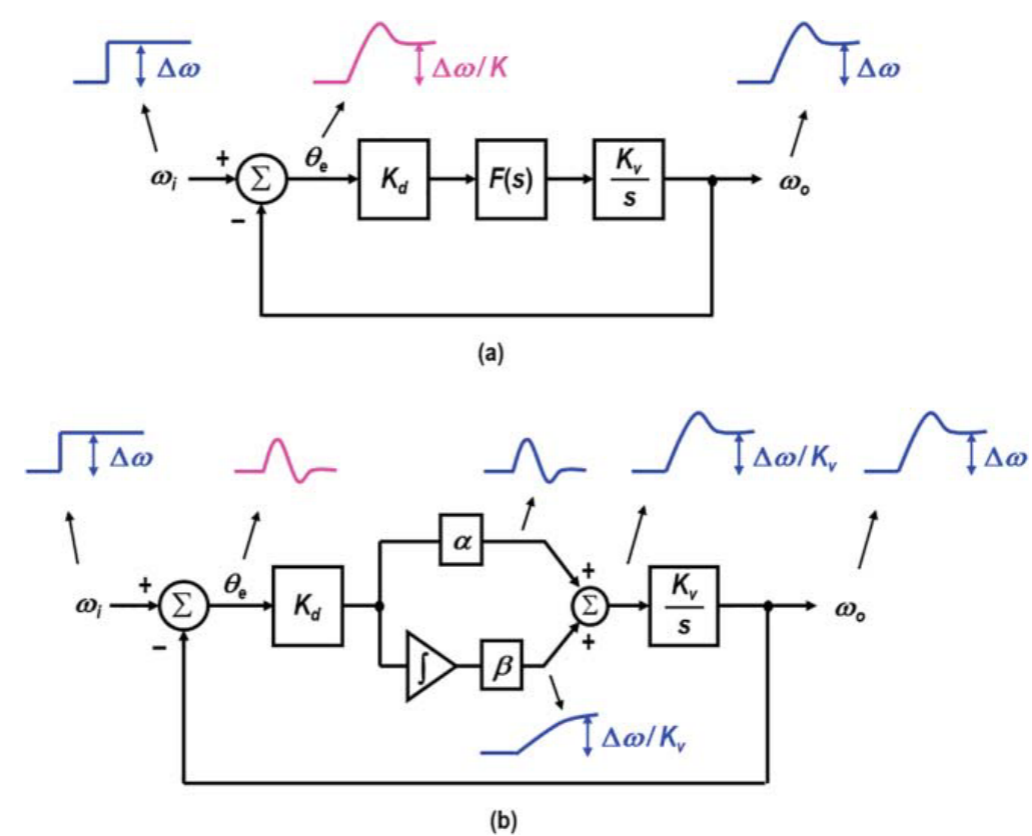

频率阶跃(type 1 和 type 2锁相环)

| (a)类型1 锁相环 | (b)类型2 锁相环 |

|

|

- 比例路径,类似于小信号路径来设置放大器增益

- 积分路径,类似于大信号路径来设置放大器的直流 工作点

状态变量模型

- 有没有可能,80%的DC信息存储在积分路径中,而剩余的DC由比例增益路径提供静态相位误差。

- 使用状态变量模型。 与仅考虑输入和输出之间的关系的传递函数模型不同,状态变量模型可以对具有积分器的反馈系统施加额外的约束。

- 为了使反馈系统稳定,积分器的输入在稳定状态下必须为零。 否则,积分器随着时间的推移累积非零输入,输出将饱和。

- 在状态变量模型中,我们通过积分器的输出定义状态变量,并施加状态变量在稳定状态下应保持恒定的约束。

- PLL的状态变量描述有助于理解内部系统参数,例如稳定状态下VCO的控制电压,这是无法用输入/输出(I/O)传递函数描述的。

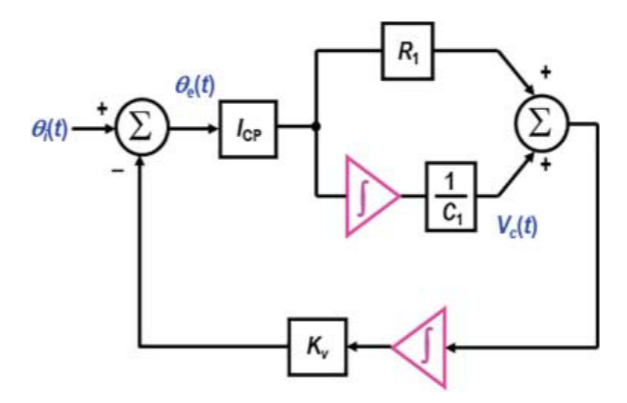

如图所示是2阶2型CPPLL状态变量模型,作为积分器输出在稳定状态下保持稳定。

状态变量方程:

对左右微分:

当系统稳态时候,稳态变量为常数,即微分为零:

解得

当输入频率阶跃:

电容中存储的稳态电压完全代表了将 VCO 频率调整相同量的输入频率变化所需的等效直流电压.

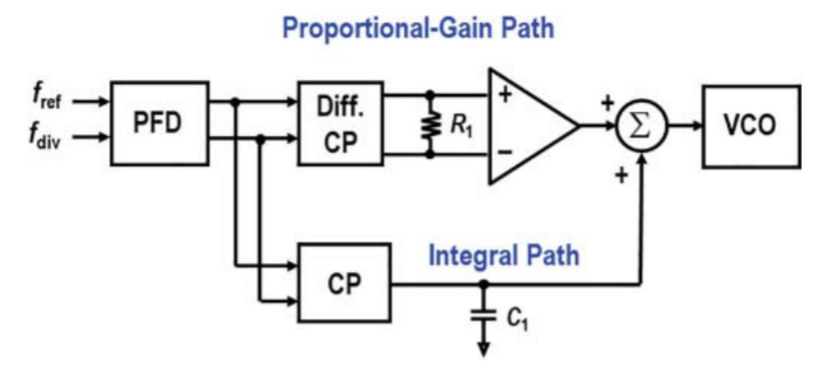

CPPLL中的两路控制

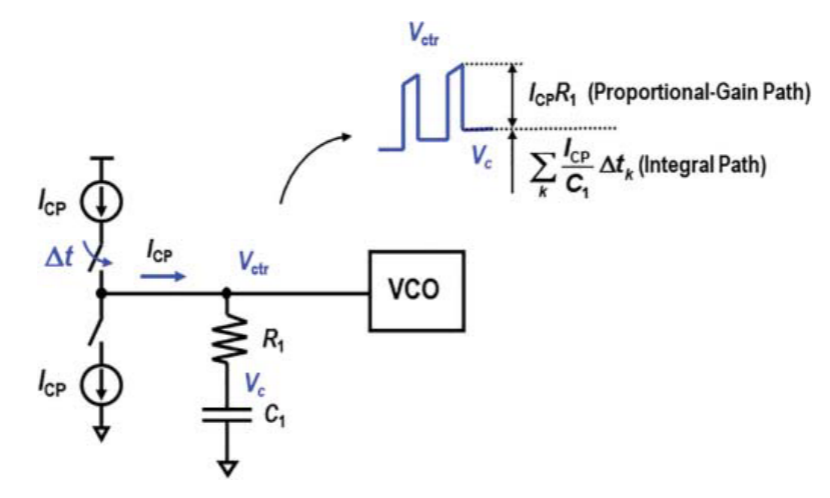

RC滤波器在type 2 PLL中的应用

- 每个参考周期,R1上的CP电流产生瞬时电压,其脉冲宽度与相位误差成正比,形成【比例路径】

- 根据相位误差的极性,正电荷or负电荷会累积在C1,形成【积分路径】

在type 2 PLL中,大 C1 使得比例路径占主导,因为 Vc(t) 不会随大 C1 变化太大。

这种情况下,环路是过阻尼,环路带宽主要由比例增益路径决定。

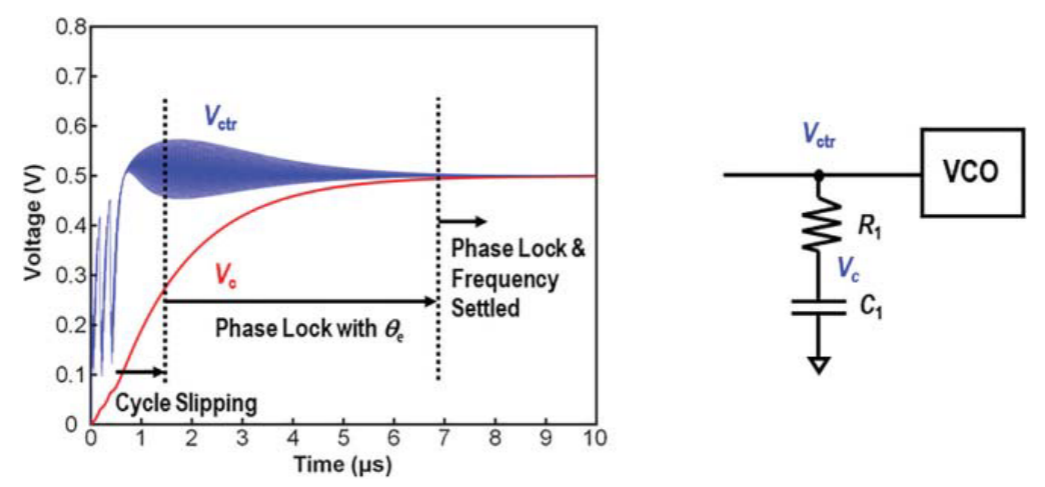

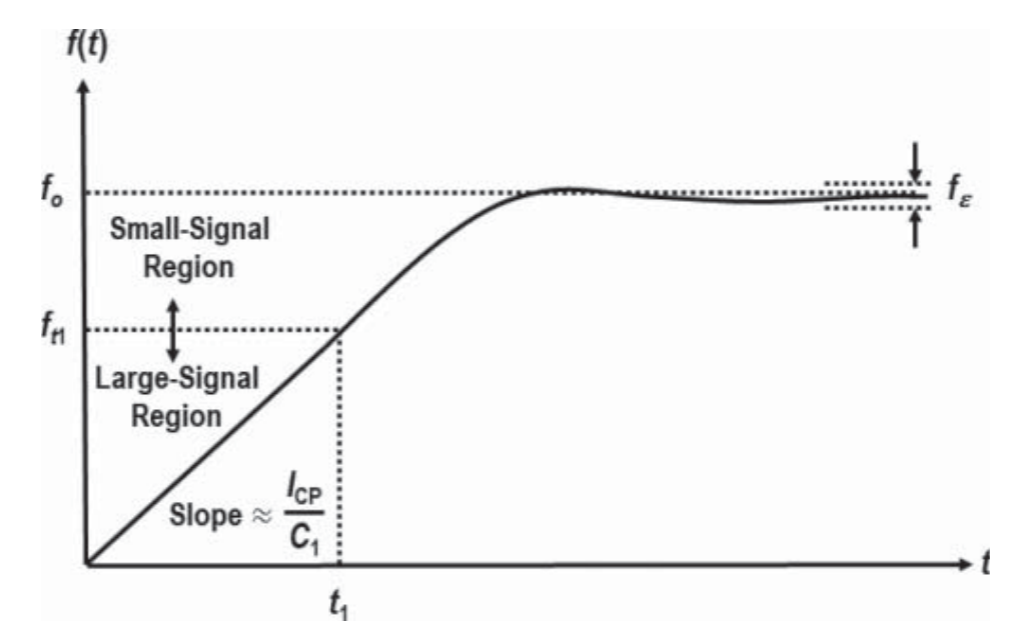

阻尼比为 2 的过阻尼三阶 2 型 CP-PLL 的模拟瞬态稳定行为

如图所示,VCO输入电压Vctr(t),电容电压Vc(t)。

- 没有观察到过冲,或纹波

- Vc(t)的稳定时间,比Vctrl(t)时间长的多

将PLL的瞬态行为定义为3个区域:

- 区域1,Vctr(t)和Vc(t)都没有稳定

- 区域2,Vctr(t)稳定,Vc(t)不稳定

- 区域2显示近锁状态,【比例路径】引起的静态相位偏移补偿调谐VCO所需剩余直流电压

- 区域2,被认为是type 1 和 type 2 环路的中间态

- 区域3,Vctr(t)和Vc(t)都稳定

- 区域3,完全稳定,PLL相位跟踪由【比例路径】控制

- 仅监视 Vctr(t) 并不是评估 2 型 CP-PLL 的稳定或静态相位误差性能的好方法,特别是对于过阻尼环路

换一种看法,

- Vc(t)代表PLL频率采集,也想PLL的DC工作点一样发挥作用

- Vctr(t) - Vc(t) 执行小信号跟踪

- Vc(t)完全稳定之后,可以正确评估 小信号参数:【相位噪声、参考杂散、静态相位误差】

双电荷泵控制

由于VCO控制电压Vctr(t)可以分解为Vc(t)和R1两端的电压,因此也可以实现双电荷泵的双路径控制。

- 为了避免共模电压,电荷泵、LPF采用差分拓扑

- 双电荷泵,可以额外控制两个电荷泵电流,环路参数提供的灵活性

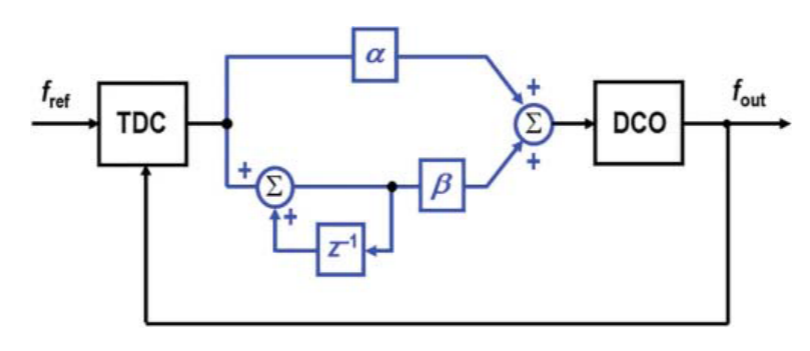

DPLL中双环路控制

了解【两个独立路径的 type 2 PLL】非常有用。

- 如果滤波器传递函数作为一个整体在数字环路滤波器(DLF)中实现,则DLF需要大量的比特来实现精确的频率控制。

- 很多比特,则延时很长,很难实现高频率分辨率

- 例如,大于14bit分辨率,则比例路径中少量比特实现快速跟踪

- 在DLF中,累加器的作用类似于CP-PLL的积分电容器C1。 数字系数𝛽设置积分路径的增益,类似于CP-PLL中的1/C1

- 数字系数 𝛼 设置比例增益路径的增益,类似于 CP-PLL 中的 R1

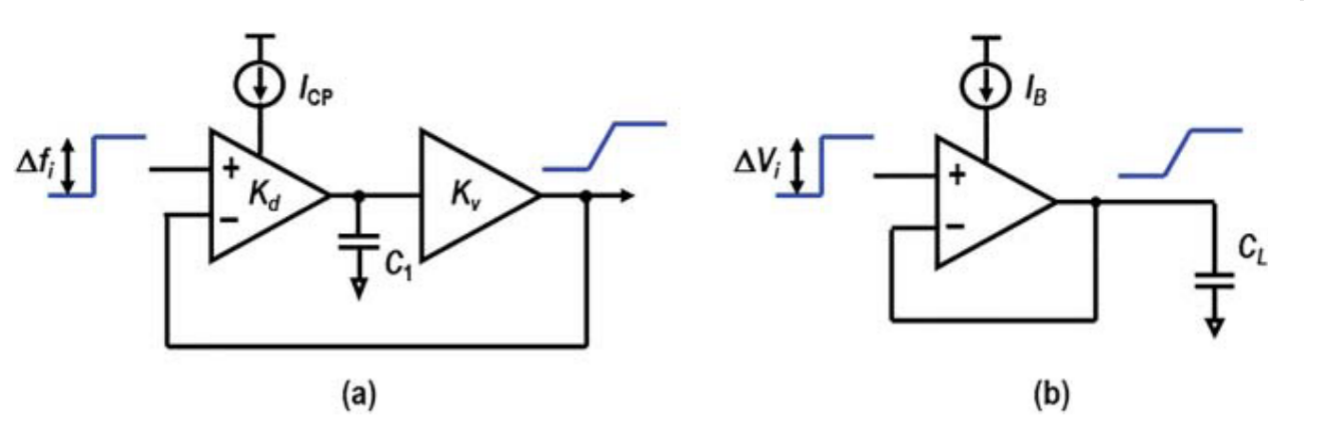

CPPLL压摆率

- 过阻尼 CP-PLL 的稳定时间受环路滤波器的积分路径(即积分电容 C1)的显着影响。

- 如果我们只考虑 PLL 锁定范围之外的频率采集,则 CP-PLL 的大信号瞬态响应主要由 C1 的充电(或放电)时间决定,因为 PFD 使电荷泵能够产生升压或降压。 脉冲取决于频率差。

- 频率采集模式下的 CP-PLL 可以被建模为一个两级放大器

- 其转换速率由 CP 电流 ICP 和 C1 决定。

- 如图所示, CP-PLL 的压摆率可以像运算放大器一样定义

- CP-PLL 的压摆率基于频率与时间比,

运算放大器的压摆率是电压与时间比

- 为了简单起见,假设 CP 电流在给定频率方向上完全导通。

- PLL 的最大转换速率 SRPLL 可以定义为

压摆率如何影响PLL锁定时间:

频率稳定函数:

:目标频率

:PLL环路常数,即 环路增益K的倒数

当没有压摆率限制时:

如果不满足上述条件,则应在稳定时间内考虑转换速率 。

则频率表达式:

则锁定范围内,PLL 稳定在频率误差 f𝜀 内的时间

所以,总的稳定时间为:

PFD开启时间影响

- 当 PFD 在周跳期间用作频率检测器时,复位延迟可能会导致增益泄漏。

- 随着比较频率的增加,增益泄漏问题变得更加显着,并且频率检测的效率在高频处进一步降低。

- 当考虑非线性稳定时间时,需要将PFD复位延迟的影响作为一个参数来考虑。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?