目录

1,概述

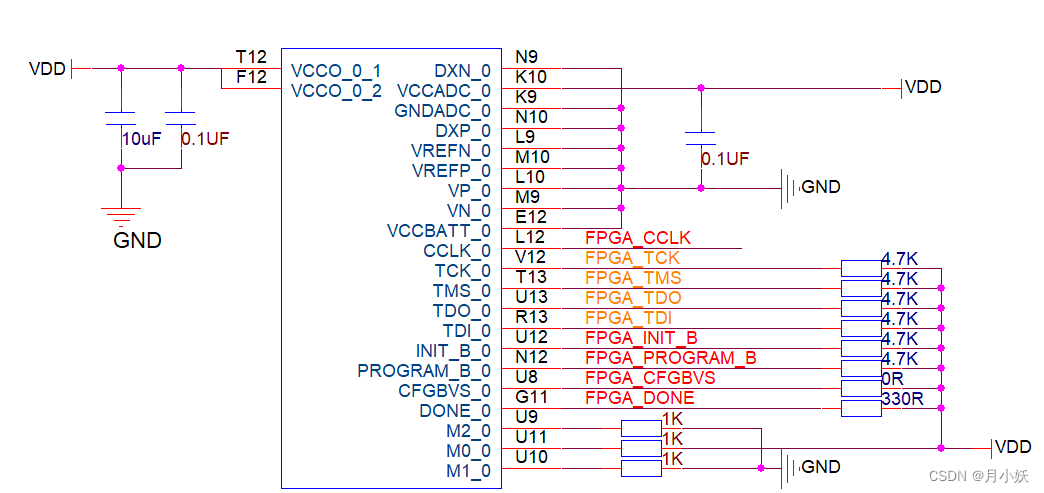

Dedicated Configuration Bank是XILINX 7系列FPGA的专用配置Bank,本文详述其深入浅出详述其功能。

2,功能详解

2.1,DXP_0与DXN_0

可以外接1个二极管型温度传感器,用于监测环境温度。DXP_0和DXN_0分别接二极管的正极和负极。当不用时,可将其接地。

2.2,VCCBATT_0

解密秘钥寄存器的备用供电,一般情况用不到,接bank供电或者接地均可。

2.3,INIT_B_0

初始化指示管脚,默认是漏极开路管脚,可根据需要将其拉低或者拉高。FPGA初始化过程这个管脚会被拉低。

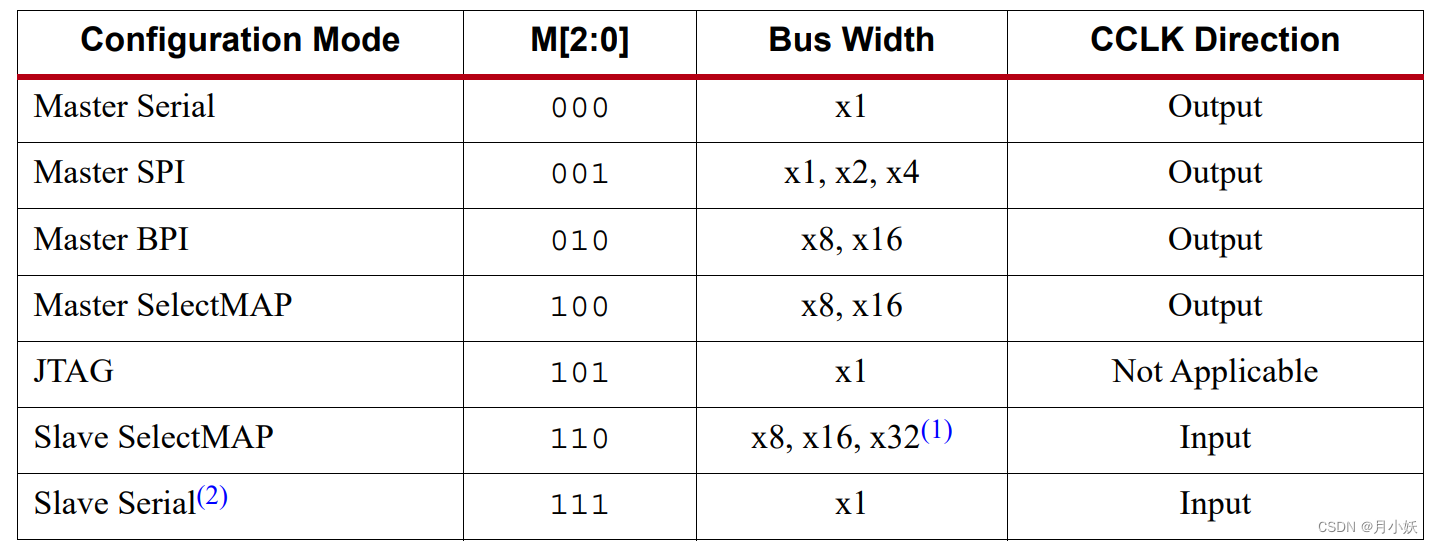

2.4,M0_0,M1_0,M2_0

配置模式选择,可以根据设计中加载程序的方法,在硬件上使用上下拉电阻,将其配置好,官方建议使用不大于1K的电阻上拉或者下拉。

2.5,TDI,TDO,TMS,TCK

JTAG测试接口,TDI数据输入,TDO数据输出,TMS片选,TCK时钟。一般情况可将TMS和TCK使用4.7K或者10K的电阻上拉。

2.6, VCCADC_0,GNDADC_0,VREFP_0,VREFN_0,VP_0,VN_0

这是内部ADC配置的一些管脚,其中GNDADC_0是ADC模拟供电的地,VCCADC_0是ADC模拟供电的电源。VREFP_0,VREFN_0是内部ADC的1.25V基准输入。VP_0,VN_0是ADC的模拟采集信号输入。

2.7, CFGBVS_0

CFGBVS_0是位于BANK0上的1个配置管脚,用于配置BANK0,BANK14,BANK15上的电压选择。如果这三个BANK的电压不小于2.5V,则该管脚须拉高到BANK0的供电。否则该管脚需要拉低到GND.如果没有用到相关管脚,所有管脚接地即可。

2.8, DONE_0

DONE_0是FPGA加载程序完成标志,当FPGA程序加载过程这个管脚会被拉低,加载完成后被拉高。

2.8, CCLK_0

该管脚是1个配置时钟管脚,当FPGA作为主外挂Flash或EEPROM时,CCLK作为时钟输出。当FPGA作为从,通过其他MCU加载程序时CCLK作为时钟输入。其是输入还是输出和M0,M1,M2配置的状态有关。

2.10,PROGRAM_B_0

FPGA的重新配置管脚,当拉低时FPGA从新读取配置,当管脚被拉高后,新的配置生效。为了放置FPGA意外重配置,该管脚需要使用4.7K的电阻上拉到BANK0的供电。

# 3,总结 FPGA的BANK0是FPGA的配置BANK,无论是硬件设计师还是逻辑设计师或者软件设计师,都应该熟悉BANK0相关的功能。

本文详细介绍了Xilinx7系列FPGA的专用配置Bank的功能,包括DXP_0与DXN_0的温度监测,VCCBATT_0的备用供电,INIT_B_0的初始化指示,M0_0,M1_0,M2_0的配置模式选择,以及JTAG接口的TDI,TDO,TMS,TCK,ADC的相关管脚,DONE_0的加载完成标志,CCLK_0的配置时钟和PROGRAM_B_0的重新配置控制等。

本文详细介绍了Xilinx7系列FPGA的专用配置Bank的功能,包括DXP_0与DXN_0的温度监测,VCCBATT_0的备用供电,INIT_B_0的初始化指示,M0_0,M1_0,M2_0的配置模式选择,以及JTAG接口的TDI,TDO,TMS,TCK,ADC的相关管脚,DONE_0的加载完成标志,CCLK_0的配置时钟和PROGRAM_B_0的重新配置控制等。

4136

4136

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?