- Byte striping: 把每个byte依次分发到不同的lane,避免不同lane传输数据长度不同

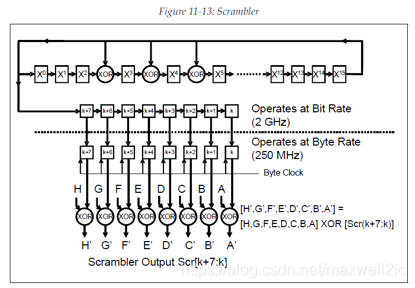

- scrambler:PRBS加扰,消除重复的pattern,因为重复的pattern在频谱上能量集中,会产生很大的EMI噪声;TLP/DLLP中的D character被scramble,而OS则不被scramble

- character:8bit uncoded byte;symbol:10bit encoded character;8b10b的作用是产生足够多的10/01变化边沿,每10个bit中不超过5个连续的0或1;接收端的decoder同时可以检测是否有symbol error;DC balancing;embedded clock;Encoding of special Control Characters;Error detection

- TX buffer根据data link layer送来packet的“Control”码来给packet加Start/End frame;TLP开头的K-character是STP,DLLP开头是SDP,good TLP/DLLP的结尾是END,bad TLP是EDB;Logical Idle sequence之后的packet的STP/SDP必须分配给lane0,如果是连续的back-to-back transmission of packet,STP/SDP必须分给0/4/8/16/32

- Ordered-Sets:多个重复的4 character sequences,开头是COM;Link training阶段,发TS1/TS2;TX周期性地发送SKIP Oerderd-Sets用于补偿TX/RX时钟频差;TX进EIDLE状态要发electrical idle OS;从L0s到L0,要发FTS。OS以K character开头,中间可能包含D character;Logical Idle Sequence在没有packe

PCIe PCS sublayer

最新推荐文章于 2025-05-19 20:20:54 发布

PCIe PCS子层负责数据的编码、加扰和时钟恢复等,包括8b10b编码、lane间的de-skew调整。8b10b编码确保数据传输中的边沿变化,防止EMI噪声。在传输过程中,TLP和DLLP的特定字符会被加扰,而数据包的开始和结束由特定的控制字符标识。Ordered-Sets用于链接训练和时钟同步,Elastic Buffer则补偿时钟频率差异。lane-to-lane deskew确保不同lane间的数据同步。

PCIe PCS子层负责数据的编码、加扰和时钟恢复等,包括8b10b编码、lane间的de-skew调整。8b10b编码确保数据传输中的边沿变化,防止EMI噪声。在传输过程中,TLP和DLLP的特定字符会被加扰,而数据包的开始和结束由特定的控制字符标识。Ordered-Sets用于链接训练和时钟同步,Elastic Buffer则补偿时钟频率差异。lane-to-lane deskew确保不同lane间的数据同步。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3837

3837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?