如下声明:

logic [7:0] data [255:0]

维度在标识符前面的部分称为packed array,在标识符后面的部分称为unpacked array,一维的pakced array也称为vector。

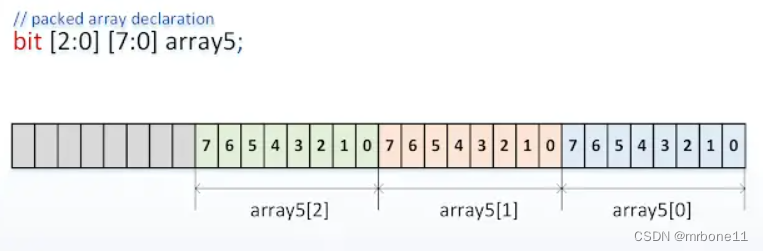

packed array

packed array只能由单bit数据类型(bit,logic,reg)、enum以及其他packed array和packed structure组成。packed array保证在内存中一定是一段连续的bit

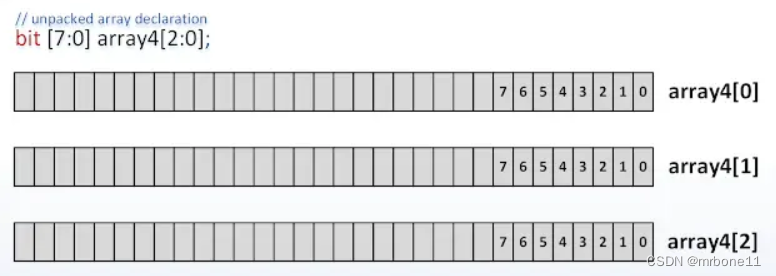

unpacked array

unpacked array的元素数据类型没有限制,unpacked array在内存中不一定是一段连续的bit

多维数组

二维数组通常被用于memory,第一维代表地址宽度,第二维代表数据宽度

如下代码:

logic [2:0][3:0] data [4:0][5:0]

这是一个什么样的数据类型呢?我们应该从unpacked dimension部分从左往右读,再从packed dimension部分从左往右读。因此这是一个[4:0][5:0][2:0][3:0]的4维数组

packed 与unpacked

enum、struct也有packed和unpacked之分。编写design时,不能将unpacked类型的数据赋值给packed类型的数据,反之亦然。

packed类型的数据其元素(成员)也必须都是recursively packed的,unpacked数据可以包含packed或者unpacked,其中packed的数据内部的元素(成员)同样必须是recursively packed的

本文讨论了逻辑数组(data)中的packedarray与unpackedarray的区别,涉及内存布局、数据类型限制,以及-packed和-unpacked在枚举和结构中的使用规则。强调了在设计中类型兼容性的重要性。

本文讨论了逻辑数组(data)中的packedarray与unpackedarray的区别,涉及内存布局、数据类型限制,以及-packed和-unpacked在枚举和结构中的使用规则。强调了在设计中类型兼容性的重要性。

600

600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?