目录

一 标量与向量(verilog)

Verilog需要表示单个位以及多个位的组。例如,一个单bit时序元件是一个触发器。然而一个16位的时序元件是一个可以容纳16位的寄存器。为此,Verilog有标量网、矢量网、变量。

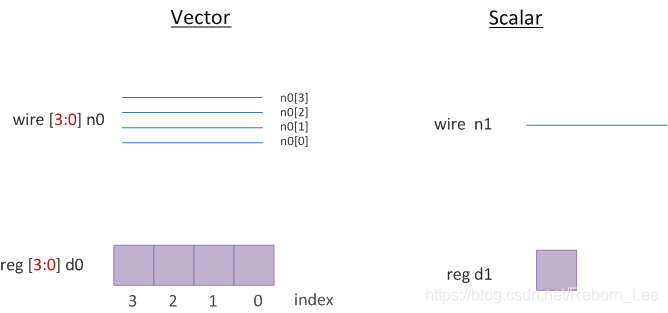

标量:一个没有指定范围的net或reg声明被认为是1位宽,是一个标量。

向量:如果指定了范围,那么net或reg就变成了一个多比特的实体,称为向量。

二 线网与变量(systemverilog)

数据对象有两组:变量和线网。

这两组不同之处在于它们被赋值和保持值的方式不同。

线网可以由一个或多个驱动连续赋值,原语输出或通过模块输出端口写入。多个驱动的结果值是由线网类型的分辨函数决定。线网不可以使用过程赋值。如果端口一侧的线网被另一侧的变量驱动,则里面隐含了一个连续赋值。force语句可以覆盖线网的值。当释放的时候,线网的值返回为原来的值。

变量可以由一个或多个过程赋值,包括过程连续赋值写入。最后写的值决定了变量里面最终的值。或者,变量可以被一个连续赋值或一个端口写入。

变量可以是其它类型的压缩或非压缩聚合(参看7.4压缩和非压缩类型)。对一个变量的独立元素进行的多个赋值分别进行检查。独立元素包括结构体的不同成员或一个数组的不同元素。压缩类型的每一个bit也是独立元素。因此,在一个压缩类型的集合中,集合中的每一个bit是一个独立元素。

左边包含一个切片的赋值将被视为对整个切片的单个赋值。因此一个结构体或数组可以其中一个元素过程赋值,另一个元素连续赋值。结构或数组的元素可以用多个连续赋值来赋值,只要每个元素不超过一个连续赋值。

精确的规则是,在一个变量的最长静态前缀的扩展中,将多个连续赋值或程序赋值和连续赋值的混合写入任何项都是错误的(最长静态前缀的定义请参见11.5.3)。

例如,假定以下的结构声明:

struct {

bit [7:0] A;

bit [7:0] B;

byte C;

} abc;以下对struct abc是合法的赋值:

assign abc.C = sel ? 8'hBE : 8'hEFnot (abc.A[0], abc.B[0]),

(abc.A[1], abc.B[1]),

(abc.A[2], abc.B[2]),

(abc.A[3], abc.B[3]);always @(posedge clk) abc.B <= abc.B + 1;以下附加语句对struct abc的赋值是非法的:

// 对abc.C的多次连续赋值

assign abc.C = sel ? 8'hDE : 8'hED;

//对abc.A[3]的混合连续赋值和过程赋值

always @(posedge clk) abc.A[3] <= !abc.B[7:3];出于上述规则的目的,已声明的变量初始化或过程性连续赋值被视为过程性赋值。force语句覆盖过程赋值语句,反过来,过程赋值语句又覆盖常规赋值。force语句既不是连续赋值也不是过程赋值。

当一个变量被连接到输入端口声明时,这就暗示是一个连续赋值。这使得对声明为输入端口的变量的赋值是非法的。当一个变量被连接到一个输出端口实例时,这就暗示是一个连续赋值。这使得对一个被连接到输出端口实例时的变量附加的过程或连续赋值非法。

变量不能被连接到一个inout端口的任何一端。变量不能在具有ref端口类型的端口之间共享。更多端口和端口连接规则参看23.3.3。

如果一个连续赋值驱动强度为除了St0,ST1,StX或Hiz的变量,编译器可能发出一个警告。在任何情况下,应该对赋值进行自动类型转换,强度消失。

不像net,一个变量不能有隐含的连续赋值作为它声明的一部分。作为一个变量声明部分的赋值是一个变量的初始化,不是一个连续赋值。

例如:

wire w = vara & varb; //具有连续赋值的net

logic v = consta & constb; //具有初始的变量

logic vw; //没有初始赋值

assign vw = vara & varb; //对一个变量连续赋值

real circ;

assign circ = 2.0 * PI * R; //对一个变量连续赋值

2474

2474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?