(2019-03-11)

平台: lattice ecp5 LFE5U-25F-BG381

关于lattice的lvds

=====================================

报错:

ERROR - par: A generic DDR interface has been locked to bank(s) 3,6, which are not neighbors; therefore, the interface cannot be covered by an ECLK signal per device architecture.

》》》 其实是

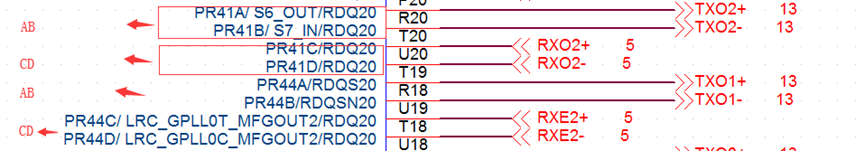

① 同一组里边的差分对,比如[7:0]lvds_o,这八对差分对(同一个lvds[7:1])只能在同一个bank中,否则就会报错。(Lattice)

② LVDS的TX只能接在BANK AB上

而RX,则可以接在BANK AB上也可以接BANK CD

=====================================

现象: lvds解出来只有de是对的,hsync和vsync是乱的,有时候de也是错的。

画面一直处于上下跳的状态

解决方法:

在lvds_rx管脚上设置内置差分电阻。 =》 完美解决

6684

6684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?