四选一多路器

下面是自己的一些理解,现在自己是一个刚进入的verilog的小白,有什么不对多写大佬提点。

题目很简单:就是四选一。

有两种解法:

- 第一种是最直接,最明显的方法,直接根据selcet选择器,所选择的对应的路,就行输出即可。

`timescale 1ns/1ns

module mux4_1(

input [1:0] d1,d2,d3,d0,

input [1:0] sel,

output [1:0] mux_out

);

reg [1:0] mux_out_reg;

always@ (*) begin

case(sel)

2'b00 : mux_out_reg <= d3;

2'b01 : mux_out_reg <= d2;

2'b10 : mux_out_reg <= d1;

2'b11 : mux_out_reg <= d0;

default : ;

endcase

end

assign mux_out = mux_out_reg;

endmodule

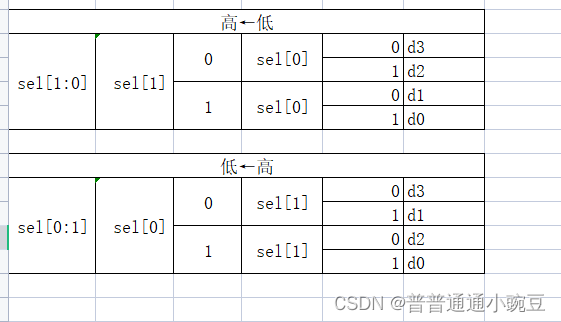

2.利用二选一多路器分解四选一多路器。

//低到高

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

assign mux_out = sel[1] ? (sel[0] ? d0:d1) : (sel[0] ? d2:d3);

endmodule

//高到低

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

assign mux_out = sel[0] ? (sel[1] ? d0:d2) : (sel[1] ? d1:d3);

endmodule

总结:

方法一:代码清晰明了,重复的代码量多,适用于路过多的,可以时钟去遍历。

方法二:代码简洁,不易理解,路少的建议使用。

上面是我的理解,自己根据自己喜欢的方式去写吧。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?