本来想用一个寄存器对输入数据进行一个时钟的缓存,但是发现对于不同方式产生的仿真数据,对应的缓存结果也不相同:

相同的代码:

`timescale 1ns / 1ps

module test(

input I_clk,

input I_rst,

input I_key

);

reg S_key_reg;

always @(posedge I_clk) begin

if (I_rst) begin

S_key_reg <= 1'b0;

end else begin

S_key_reg <= I_key;

end

end

endmodule

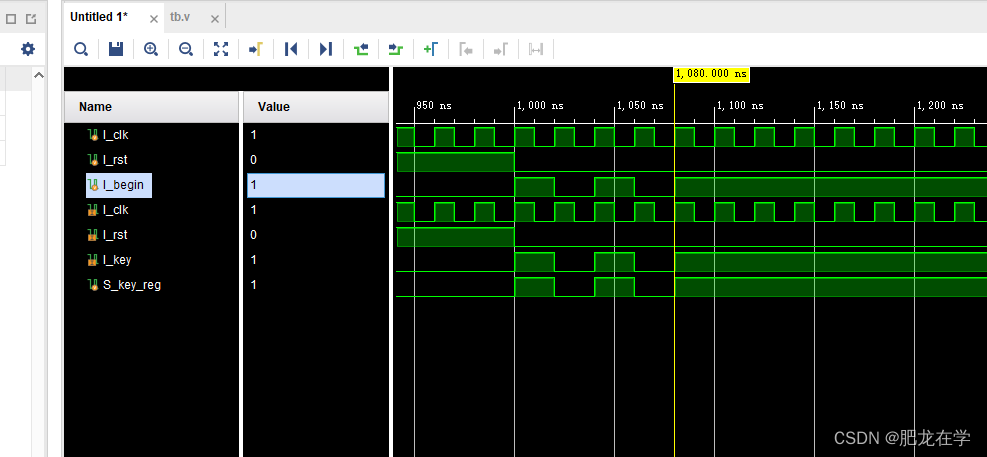

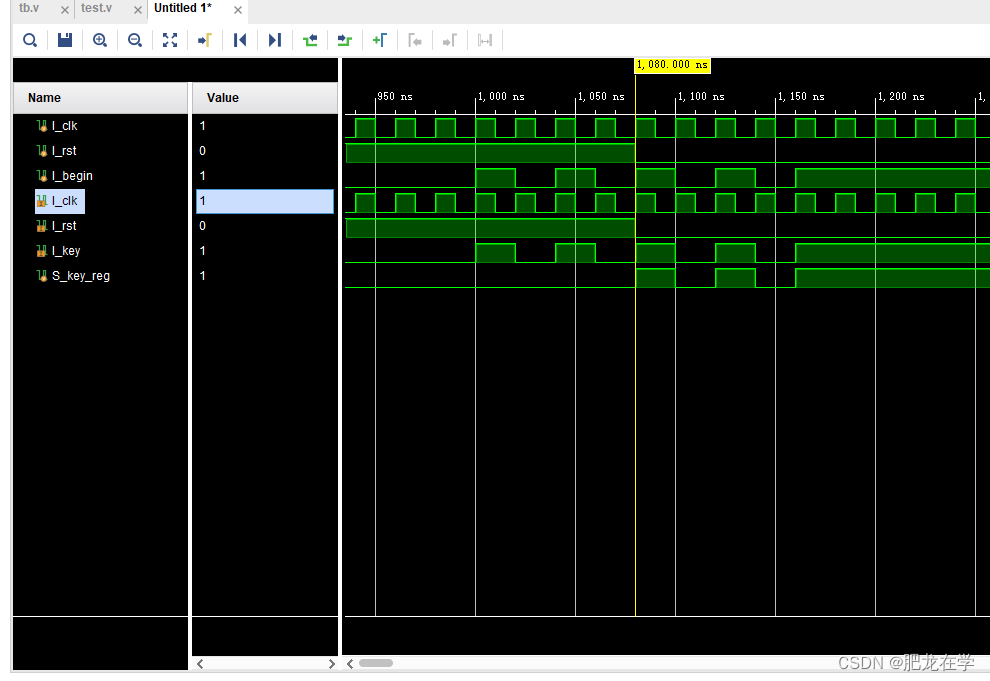

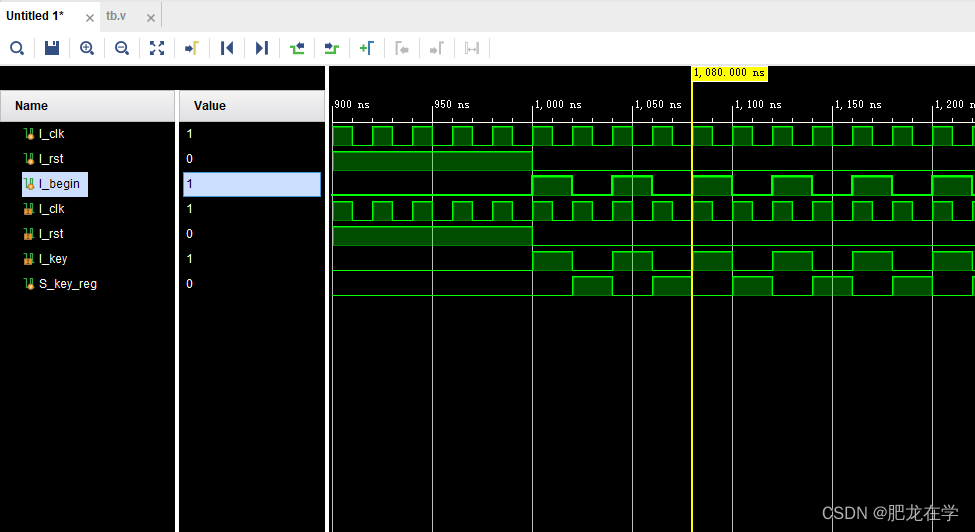

一:采用#20方式进行赋值输入:(在时钟上升沿输入不可缓存,在时钟下降沿输入可以实现缓存)

`timescale 1ns / 1ps

module tb( );

reg I_clk;

reg I_rst;

reg I_begin;

initial begin

I_clk = 1'b1;

I_rst = 1'b1;

I_begin = 5'd0;

#1000

I_rst = 1'b0;

I_begin = 1'd1;

#20

I_begin = 1'd0;

#20

I_begin = 1'd1;

#20

I_begin = 1'd0;

#20

I_begin = 1'd1;

end

test test(

.I_clk (I_clk),

.I_key (I_begin),

.I_rst (I_rst)

);

always #10 I_clk = ~I_clk;

endmodule

`timescale 1ns / 1ps

module tb( );

reg I_clk;

reg I_rst;

reg I_begin;

initial begin

I_clk = 1'b1;

I_rst = 1'b1;

I_begin = 5'd0;

#1010

I_rst = 1'b0;

I_begin = 1'd1;

#20

I_begin = 1'd0;

#20

I_begin = 1'd1;

#20

I_begin = 1'd0;

#20

I_begin = 1'd1;

end

test test(

.I_clk (I_clk),

.I_key (I_begin),

.I_rst (I_rst)

);

always #10 I_clk = ~I_clk;

endmodule

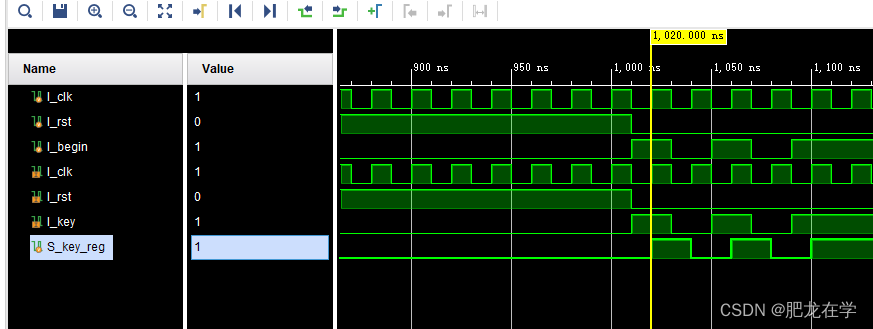

二:采用抓取时钟上升沿进行递加赋值输入:(可以实现缓存)

`timescale 1ns / 1ps

module tb( );

reg I_clk;

reg I_rst;

reg I_begin;

initial begin

I_clk = 1'b1;

I_rst = 1'b1;

I_begin = 5'd0;

end

always @(posedge I_clk) begin

if (I_rst) begin

I_begin <= 1'b0;

end else begin

I_begin <= I_begin+1;

end

test test(

.I_clk (I_clk),

.I_key (I_begin),

.I_rst (I_rst)

);

always #10 I_clk = ~I_clk;

endmodule

目前不知道原因

3077

3077

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?