什么是feedthrough 什么是pipeline?

1.feedthrough脚本

set fts_prefix "MY_FEEDTHROUGH"

set fts_buf_ref "HDBLVT08_BUF_8"

### fts

# WDATAS[108]

set net_name "WDATAS[108]"

set from_inst_name "g_ca53_cpu_2__u_ca53_cpu"

set to_inst_name "u_ca53_l2"

create_port -design "ca53_cpu_frame.nlib:ca53_cpu.design" -direction in -port_type signal "${fts_prefix}_PORT_3_1_IN_${net_name}"

create_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_IN_${net_name}"

create_port -design "ca53_cpu_frame.nlib:ca53_cpu.design" -direction out -port_type signal "${fts_prefix}_PORT_3_1_OUT_${net_name}"

create_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_OUT_${net_name}"

create_cell -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_INST_3_1_BUF_WDATAS_108" $fts_buf_ref

connect_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_IN_${net_name}" "${fts_prefix}_PORT_3_1_IN_${net_name}"

connect_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_OUT_${net_name}" "${fts_prefix}_PORT_3_1_OUT_${net_name}"

connect_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_IN_${net_name}" "${fts_prefix}_INST_3_1_BUF_WDATAS_108/A"

connect_net -design "ca53_cpu_frame.nlib:ca53_cpu.design" "${fts_prefix}_NET_3_1_OUT_${net_name}" "${fts_prefix}_INST_3_1_BUF_WDATAS_108/X"

set net_driver [get_ports -of [get_nets $net_name] -filter "direction==in"]

set net_load [get_pin -of [get_nets $net_name] -filter "direction==in"]

disconnect_net $net_name $net_load

connect_net $net_name ${from_inst_name}/${fts_prefix}_PORT_3_1_IN_${net_name}

create_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} ${from_inst_name}/${fts_prefix}_PORT_3_1_OUT_${net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} $net_load

# WDATAS[106]

set net_name "WDATAS[106]"

set reuse_net_name "WDATAS[108]"

set from_inst_name "g_ca53_cpu_0__u_ca53_cpu"

set to_inst_name "u_ca53_l2"

set net_driver [get_ports -of [get_nets $net_name] -filter "direction==in"]

set net_load [get_pin -of [get_nets $net_name] -filter "direction==in"]

disconnect_net $net_name $net_load

connect_net $net_name ${from_inst_name}/${fts_prefix}_PORT_3_1_IN_${reuse_net_name}

create_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} ${from_inst_name}/${fts_prefix}_PORT_3_1_OUT_${reuse_net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} $net_load

# WDATAS[104]

set net_name "WDATAS[104]"

set reuse_net_name "WDATAS[108]"

set from_inst_name "g_ca53_cpu_3__u_ca53_cpu"

set to_inst_name "u_ca53_l2"

set net_driver [get_ports -of [get_nets $net_name] -filter "direction==in"]

set net_load [get_pin -of [get_nets $net_name] -filter "direction==in"]

disconnect_net $net_name $net_load

connect_net $net_name ${from_inst_name}/${fts_prefix}_PORT_3_1_IN_${reuse_net_name}

create_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} ${from_inst_name}/${fts_prefix}_PORT_3_1_OUT_${reuse_net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} $net_load

# WDATAS[102]

set net_name "WDATAS[102]"

set reuse_net_name "WDATAS[108]"

set from_inst_name "g_ca53_cpu_1__u_ca53_cpu"

set to_inst_name "u_ca53_l2"

set net_driver [get_ports -of [get_nets $net_name] -filter "direction==in"]

set net_load [get_pin -of [get_nets $net_name] -filter "direction==in"]

disconnect_net $net_name $net_load

connect_net $net_name ${from_inst_name}/${fts_prefix}_PORT_3_1_IN_${reuse_net_name}

create_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} ${from_inst_name}/${fts_prefix}_PORT_3_1_OUT_${reuse_net_name}

connect_net ${fts_prefix}_NET_${from_inst_name}_${to_inst_name}_1_3_${net_name} $net_load

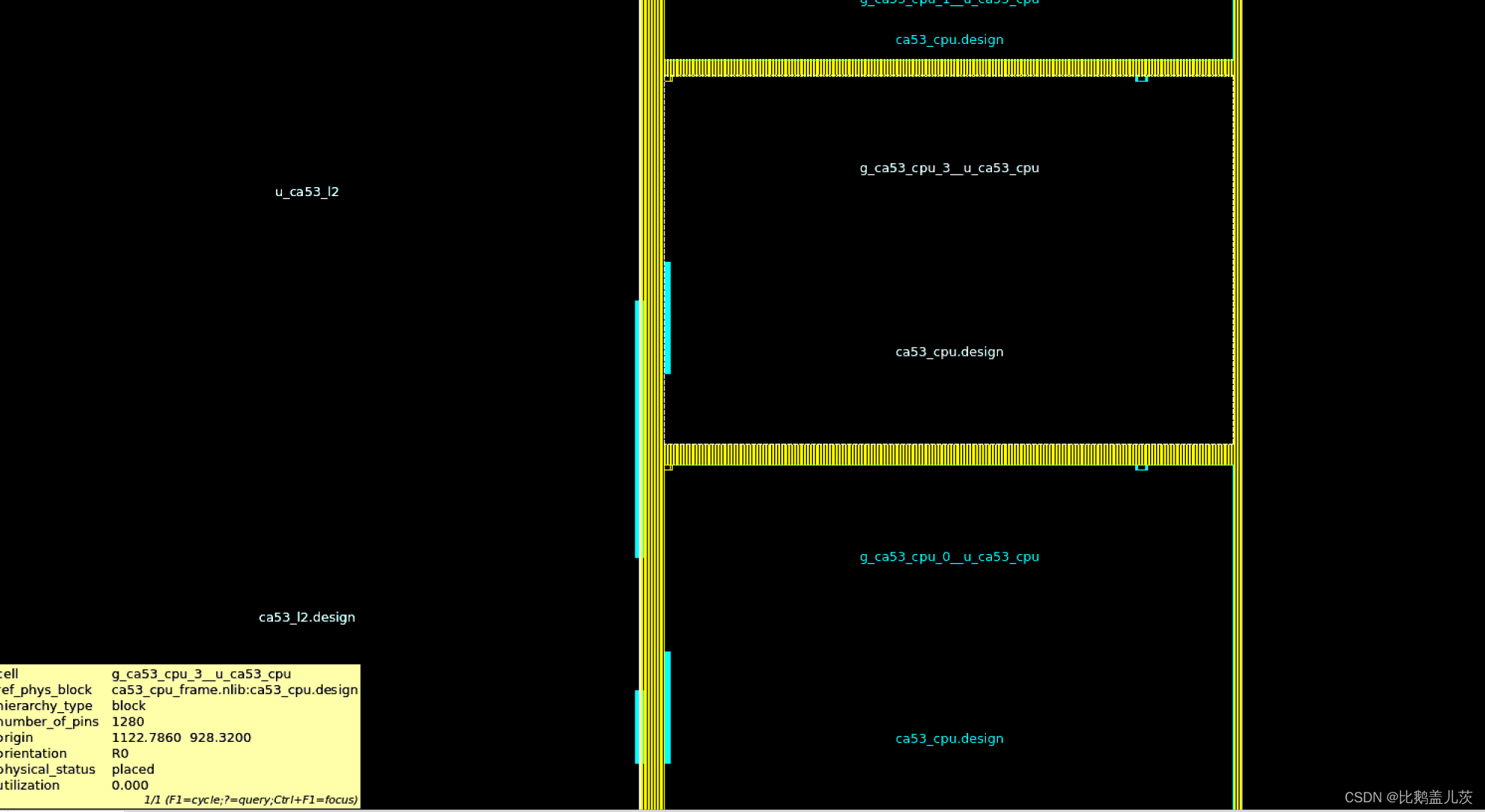

2.结果

电源规划

1.load upf

分别对block 和 top load

### load upf

set_app_options -name mv.upf.enable_golden_upf -value true

foreach _block [get_attr [get_blocks -hier] full_name] {

set_working_design_stack ${_block}

set block_name [get_att [current_block] name]

set_app_options -name mv.upf.enable_golden_upf -value true

reset_upf

load_upf data/blocks/${block_name}.golden.upf

commit_upf

connect_pg_net

save_block

set_working_design_stack CORTEXA53_stub.nlib:CORTEXA53.design

}

set_working_design_stack CORTEXA53_stub.nlib:CORTEXA53.design

reset_upf

load_upf data/CORTEXA53.golden.upf

commit_upf

connect_pg_net -all_blocks -automatic

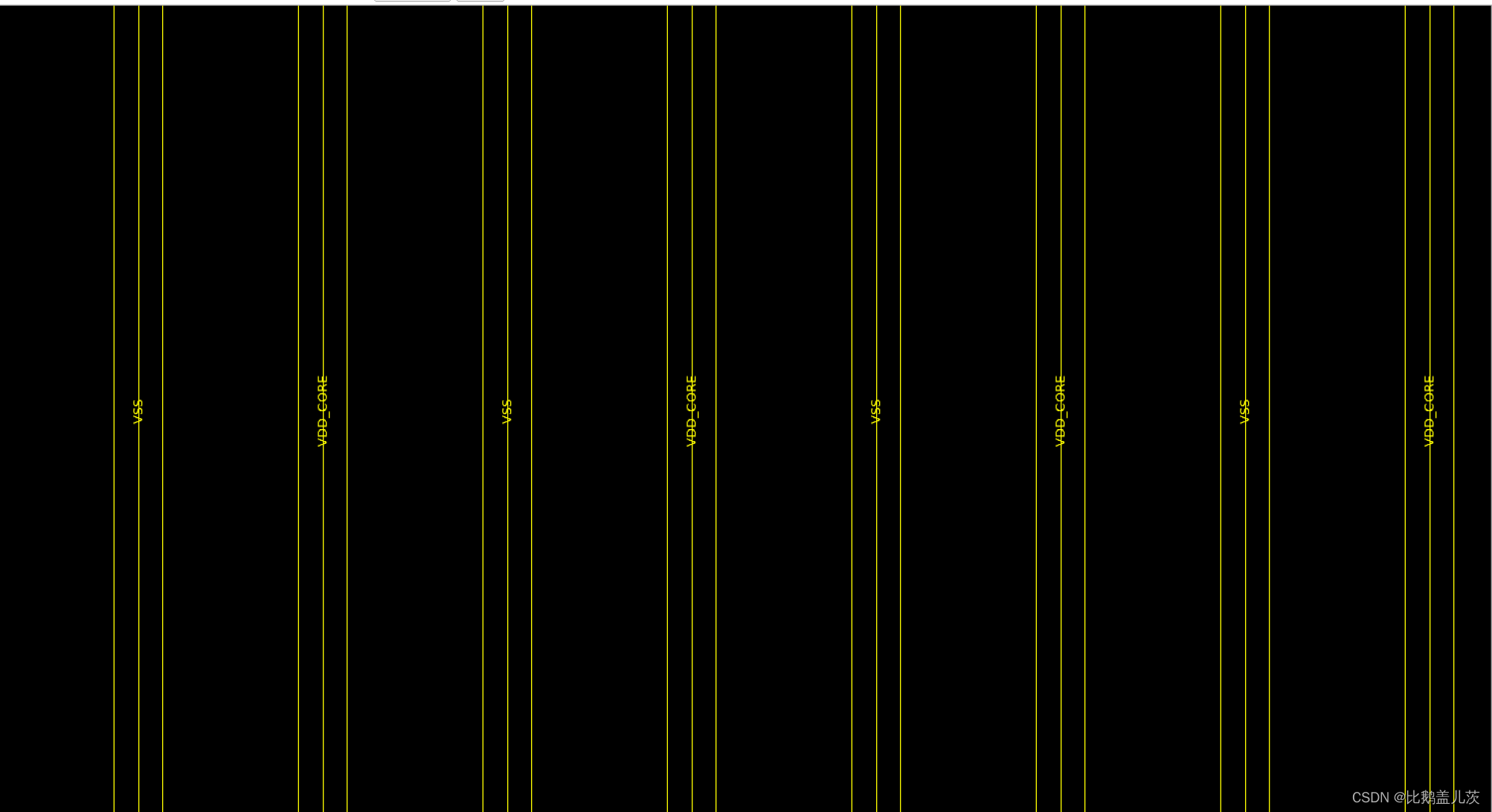

2.创建pg net/wire

### create pg wires/vias

create_pg_wire_pattern pattern_stripe_offtrack \

-layer @l -direction @d -width @w -spacing @s -pitch @p \

-parameters {l d w s p }

create_pg_composite_pattern PATTERN_M11_PWR_MESH -nets {VDD_CORE } -add_patterns {{{pattern: pattern_stripe_offtrack} {nets: {VDD_CORE }} {parameters: {M11 vertical 0.36 1.008 2.736 }}{offset: {1.14 0}}}}

create_pg_composite_pattern PATTERN_M11_GND_MESH -nets {VSS } -add_patterns {{{pattern: pattern_stripe_offtrack} {nets: {VSS }} {parameters: {M11 vertical 0.36 0 2.736 }}{offset: {2.508 0}}}}

set_pg_strategy STRATEGY_M11_PWR_MESH -pattern {{name: PATTERN_M11_PWR_MESH} {nets: {VDD_CORE }}} -design_boundary

set_pg_strategy STRATEGY_M11_GND_MESH -pattern {{name: PATTERN_M11_GND_MESH} {nets: {VSS }}} -design_boundary

compile_pg -strategies { STRATEGY_M11_PWR_MESH STRATEGY_M11_GND_MESH }

set_app_options -name plan.pins.new_cell_name_tag -value ""

set_app_options -name plan.pins.new_port_name_tag -value ""

set top_shapes [get_shapes -of [get_nets -filter "net_type==power||net_type==ground" -quiet] -filter "layer.name==M11" -quiet]

if { $top_shapes != "" } {

push_down_objects -cells {u_ca53_l2 g_ca53_cpu_0__u_ca53_cpu} $top_shapes

} else {

echo "MY-Error: Failed to find pg shapes to push down"

}

结果

用push down 把blockd电源线打进去

注意:block要对齐!,否则打电源线会出问题

写出data

### top def

set top_block [get_att [current_block] full_name]

set design [get_att [get_blocks $top_block] top_module_name]

set dataout_dir data/out

file mkdir $dataout_dir

set target_objects ""

append_to_col target_objects [get_cells -physical_context -filter "(is_hard_macro==true||is_soft_macro==true)&&physical_status!=unplaced" -quiet]

append_to_col target_objects [get_ports *]

write_def $dataout_dir/${design}.floorplan.def -version 5.8 -compress gzip -include_tech_via_definitions -include {rows_tracks cells ports} \

-objects $target_objects

### block def (size, pin location, special IP location)

set sub_blocks [get_blocks -hier -all]

foreach_in_col _block $sub_blocks {

set block_stack [get_att ${_block} full_name]

set block_name [get_att ${_block} name]

set_working_design_stack $block_stack

# block def

set output_file "$dataout_dir/${block_name}.floorplan.def"

write_def $output_file -version 5.8 -compress gzip -include_tech_via_definitions -include {rows_tracks cells ports}

# block netlist (necessry when feedthrough, pipeline register eco are added)

# set output_file "$dataout_dir/${block_name}.vnet.gz"

# write_verilog $output_file -compress gzip -exclude {leaf_module_declarations end_cap_cell well_tap_cell filler_cells}

# set_working_design_stack $top_block

}

1740

1740

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?