如何减少PCB的插入损耗:从材料、设计到工艺的全流程优化

目录

一、插入损耗的基础理论与核心影响因素

1.1 插入损耗的定义与物理本质

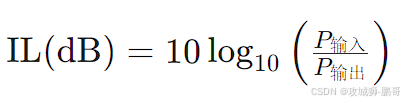

插入损耗(Insertion Loss, IL)是指信号在PCB传输路径中因能量损耗导致的功率衰减,通常用分贝(dB)表示,计算公式为:

其本质是信号能量在传输过程中被转换为热能、电磁辐射或反射回源端的能量,主要由以下五部分组成:

- 电阻损耗:导体(铜箔)的直流电阻和高频趋肤效应导致的损耗

- 介质损耗:绝缘材料(基材)的介电损耗和极化损耗

- 辐射损耗:电磁场泄漏到空间的能量损失

- 反射损耗:阻抗不匹配导致的信号反射

- 耦合损耗:相邻传输线间的串扰导致的能量耦合

1.2 高频场景下的损耗加剧效应

在高速数字信号(如10Gbps以上)或射频信号(1GHz以上)传输中,插入损耗随频率升高呈指数增长,主要原因包括:

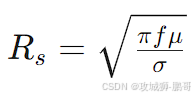

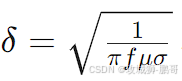

- 趋肤效应:导体有效导电截面积随频率升高而减小,表面电阻

增加(f 为频率,μ 为磁导率,σ为电导率)

- 介质极化:高频下绝缘材料的偶极子极化滞后于电场变化,损耗角正切(( \tan\delta ))显著影响能量损耗

- 寄生参数:过孔、焊盘、连接器等结构的寄生电感(( L ))和电容(( C ))导致阻抗波动和谐振效应

二、材料选择:从基材到导体的低损耗设计

2.1 基材介电常数与损耗角正切的优化

2.1.1 低损耗基材的对比与选型

绝缘材料的损耗角正切(( \tan\delta ))是影响介质损耗的关键参数,下表对比了典型PCB基材的性能:

| 材料类型 |

介电常数(ϵr, 1GHz) |

损耗角正切((tanδ, 1GHz) |

适用频率范围 |

成本对比 |

| FR-4(普通) |

4.2-4.8 |

0.020-0.035 |

<1GHz |

低 |

| FR-4(低损耗) |

4.2-4.5 |

0.015-0.020 |

1-3GHz |

中低 |

| 罗杰斯4350B |

3.48 |

0.0037 |

1-20GHz |

中高 |

| 聚四氟乙烯(PTFE) |

2.1-2.6 |

0.0009-0.002 |

>20GHz |

高 |

| 高速PPO/LCP |

2.8-3.5 |

0.004-0.008 |

5-15GHz |

中高 |

设计建议:

- 当频率>10GHz时,优先选择PTFE或高频陶瓷基材料(如Rogers RO4003C),( tanδ < 0.005 )

- 中高频场景(1-10GHz)可选用改性环氧树脂(如Isola 370HR)或LCP材料,平衡损耗与成本

- 低频场景(<1GHz)使用普通FR-4,但需注意厚度均匀性对阻抗的影响

2.1.2 介质厚度与叠层结构的优化

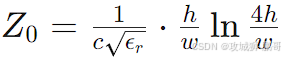

较薄的介质层可降低传输线特性阻抗(

,微带线公式),但会增加边缘场辐射损耗。建议:

- 高速差分线采用对称叠层,介质厚度控制在50-100μm,避免厚度波动>5%

- 多层板内层使用预浸料(Prepreg)时,选择低孔隙率型号(孔隙率<1%),减少介质不均匀性

2.2 导体材料与表面处理优化

2.2.1 铜箔粗糙度对趋肤效应的影响

铜箔表面粗糙度(用轮廓算术平均偏差 ( R_a ) 表示)直接影响高频有效导电面积,下表对比不同铜箔的性能:

| 铜箔类型 |

粗糙度 ( R_a (μm) ) |

表面电阻(10GHz, mΩ/cm) |

成本对比 |

| 电解铜箔(ED) |

1.5-3.0 |

8-12 |

低 |

| 压延铜箔(RA) |

0.5-1.0 |

5-8 |

中高 |

| 超低粗糙度(VLP) |

0.2-0.4 |

3-5 |

高 |

机理分析:当频率>1GHz时,趋肤深度

小于铜箔粗糙度(如10GHz时 δ≈1.6μm),粗糙表面会增加电流路径长度,导致损耗上升。

设计建议:

- 高频传输线(>5GHz)优先使用RA或VLP铜箔,降低表面电阻30%-50%

- 普通信号可使用ED铜箔,但需控制粗糙度 ( R_a < 2.5μm )

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1215

1215

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?