一、fpga的时钟资源

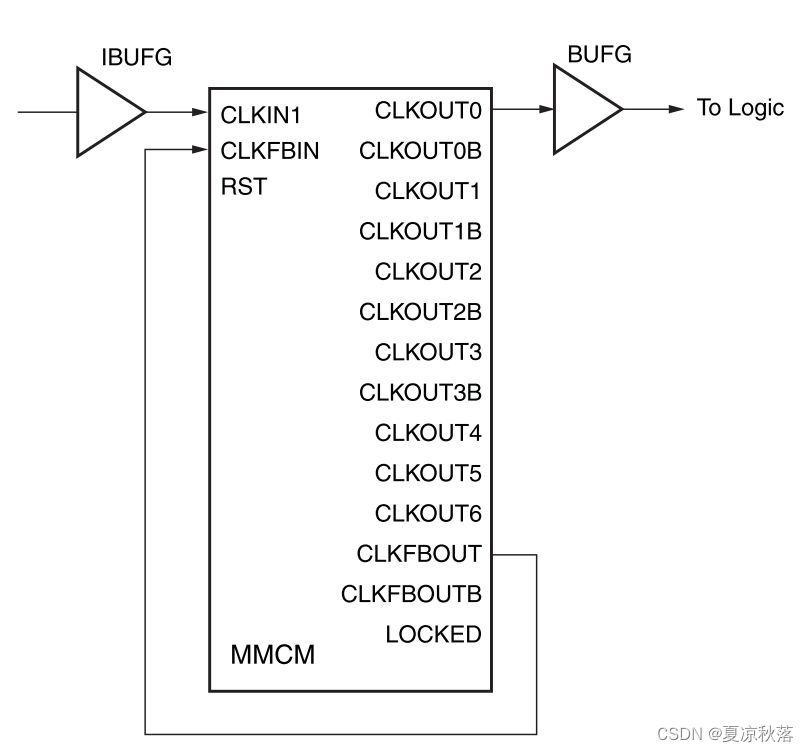

7系列FPGA里,每一个时钟区域对应一个CMT(clock management tile),CMT由1个MMCM(mixed-mode clockmanager)和1个PLL(phase-locked loop)组成,如下图所示为其输入/输出连接图。

MMCM、PLL的功能可以总结为3点:

(1) 频率综合:将外部输入的固定频率时钟调理成多路不同频率的时钟

(2) 去抖动

(3) 去偏斜

(4) 相位操作

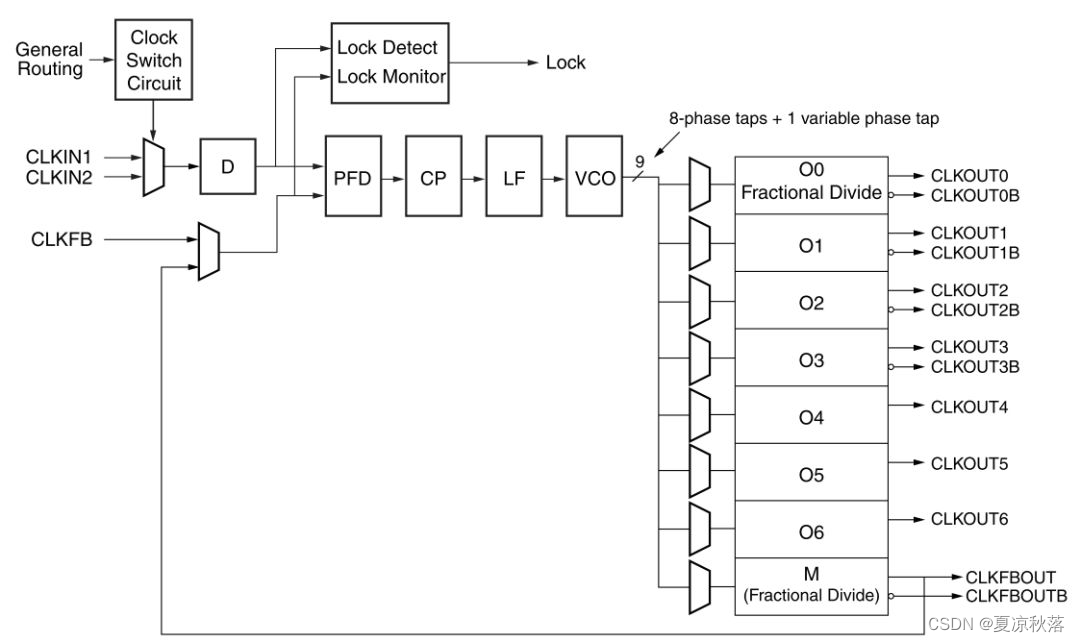

咱们这里强调下,7系列FPGA里的PLL只是MMCM的功能子集。这里咱们先介绍MMCM,下图所示为其结构框图:

上图咱们一目了然,MMCM有2个时钟输入,使用时任选1路即可,输入时钟经过PFD(phase-frequency detector),CP(charge pump),LF(loop filter)后产生一定幅度的电压输入到VCO,VCO产生频率与输入电压幅度成比例的高频时钟,再除以M倍并反馈到PFD。因此VCO的输出频率是一个稳定的、输入频率M倍的高频时钟,该时钟除以不同的倍数(用户可调)即可输出时钟clkout0~~clkout6。另外第0路输出和反馈输出是可以被分数除法,且第0路~第3路提供反相180度的输出,VCO的输出还可以精确调整相位,这是7系列FPGA特有的。

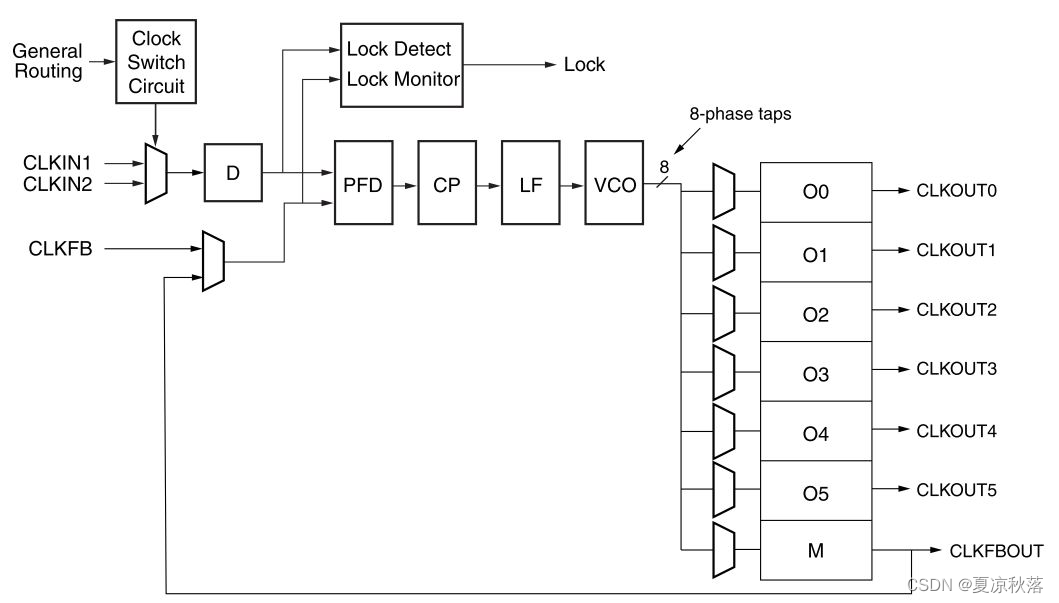

咱们再看PLL的结构,如图3所示:

其结构与MMCM大体一致,但没有反相输出、分数倍数的除法、精确的动态相位调整以及CLKOUT6。

这里强调一下:MMCM、PLL均可实现时钟整数倍的频率综合、去抖、去偏斜,但MMCM还可以实现分数倍的频率综合、反相时钟输出以及动态的时钟相位调整。当然,对于咱们一般的应用来说,用不到MMCM的这些高端功能,两者使用没啥区别。

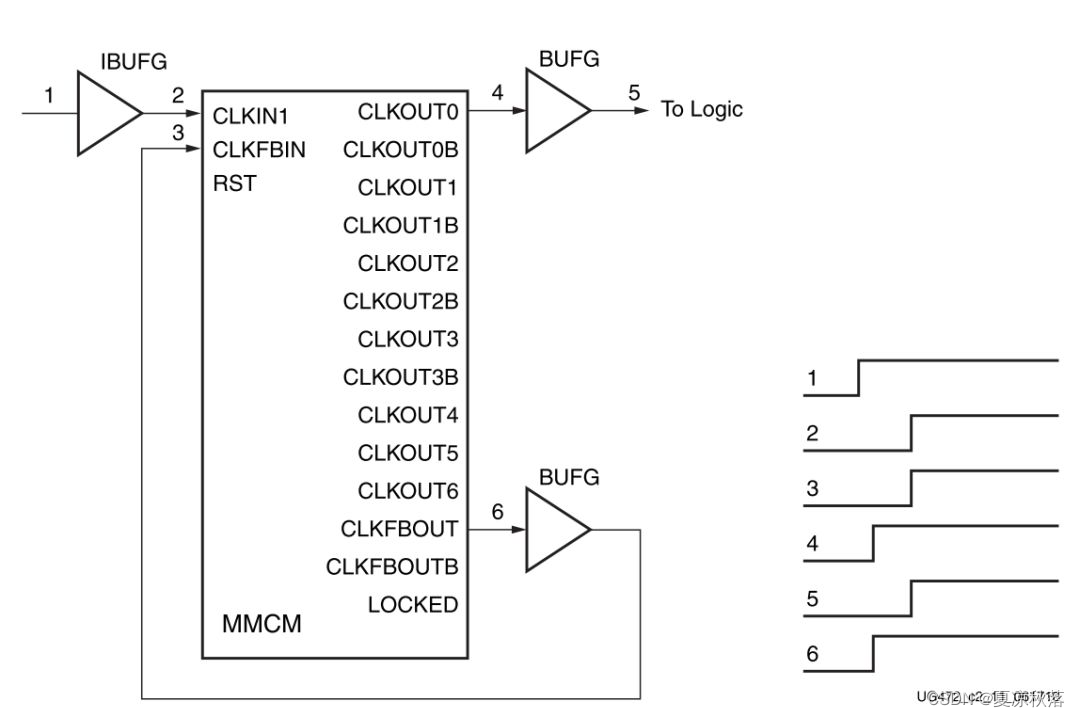

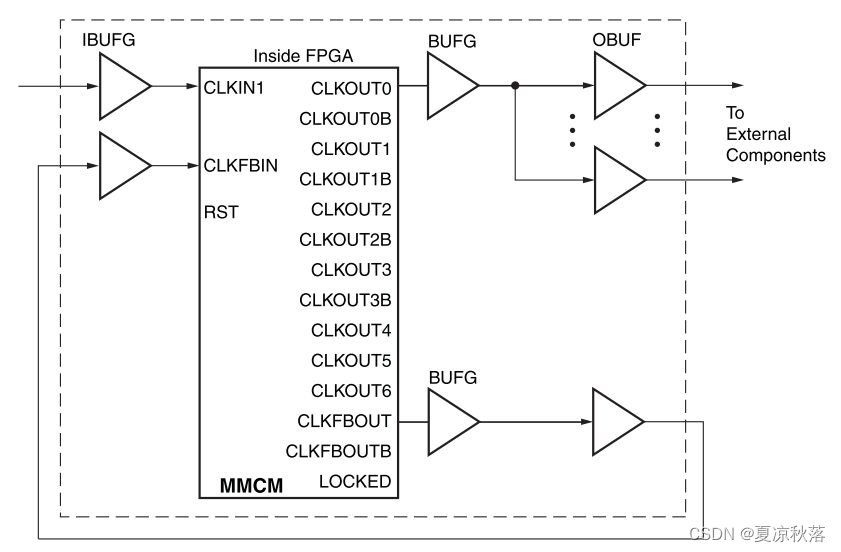

接下来咱们给出xilinx官方推荐的几种MMCM/PLL的使用方法:

被使用的最多,这种方式设计保留了输入与输出时钟之间的相位关系,时钟性能最高,系统最稳定,但需要使用2个BUFG,BUFG在FPGA里面属于稀缺资源,只有32个,对于某些特别复杂的系统可能就捉襟见肘了。

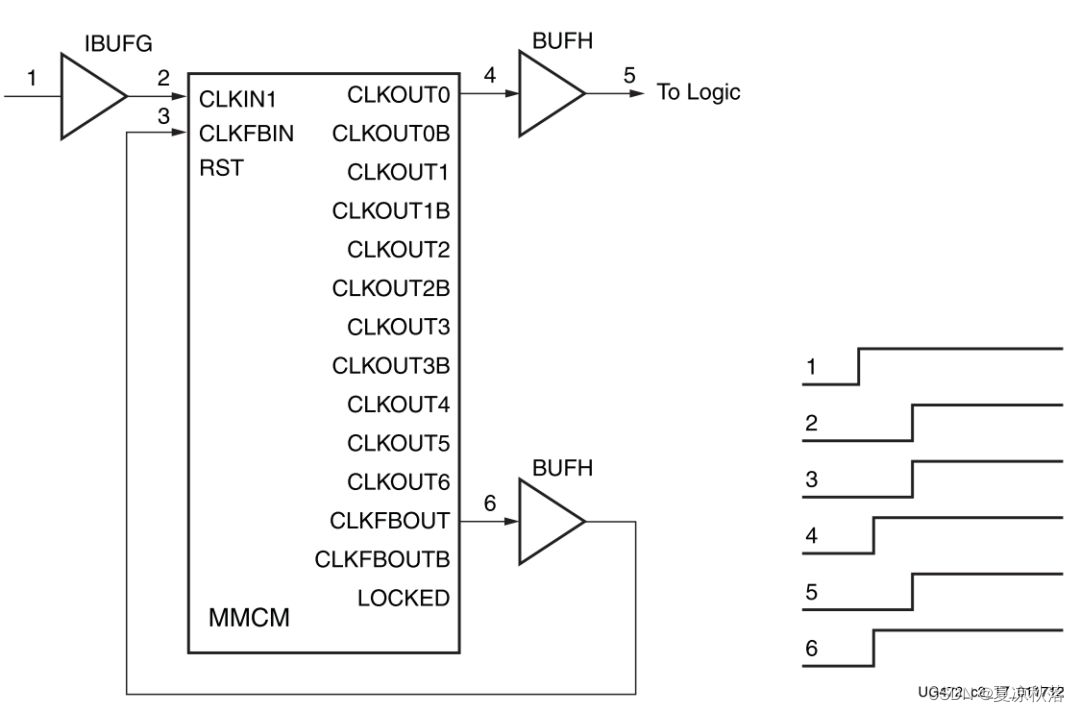

下图将BUFG换成了BUFH,其系统性能是优于BUFG的,但前一篇咱们提到过,BUFH的使用范围只有左右相邻的时钟区域,对于逻辑资源使用量超过2个时钟区域的应用肯定就不合适了。

下图为时钟的内部反馈应用,由于没有引入BUFG反馈的噪声,因此输出时钟的噪声性能更好,但失去了输入与输出时钟之间的相位关系,所有这种用法适用于高精度的频率综合,对相位关系不太关注的应用。

下图为零延迟的时钟应用,这种应用适用于单个外部时钟源供给需要保持相位关系的多个数字系统。

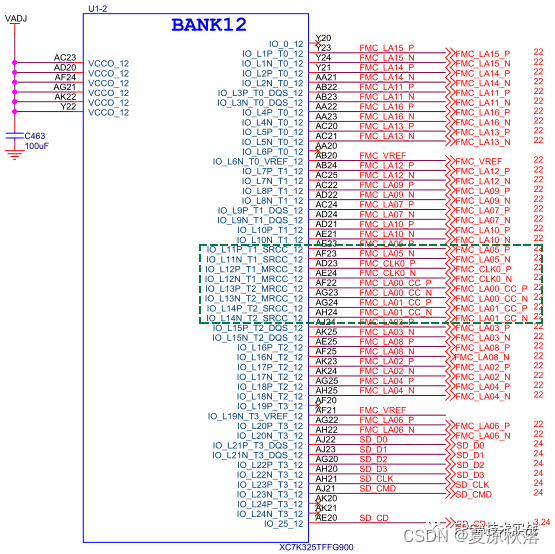

二、CLOCK_DEDICATED_ROUTE

外部用户时钟必须通过称为clock-capable(CC)输入的差分时钟管脚对引入FPGA。时钟输入管脚支持对内部全局和区域时钟资源的专用高速访问。时钟输入管脚使用专用路由,必须用于时钟输入,以保证各种时钟的时序特征。使用本地互联的一般目的I/O不应用于时钟信号。

图中可以看出每个I/O bank中每个I/O组中的50个I/O管脚中,有4个支持时钟的输入管脚对(共8个管脚)。每个时钟输入:

可连接到PCB上的差分或单端时钟

可为任何I/O标准配置,包括差分I/O标准

有一个P-side(主)和一个N-side(从)

如果单端时钟连接到差分时钟管脚对的P侧,则N侧不能用作另一个单端时钟管脚,它只能用作用户I/O。时钟输入管脚在每个I/O Bank中有2个MRCCs和2个SRCCs对。SRCC访问单个时钟区域和全局时钟树,以及同一列中上下的其他CMTs。SRCC可以驱动:

同一时钟区域内的区域时钟线(BUFR、BUFH、BUFIO)。

同一时钟区域和相邻时钟区域的CMT。

位于器件的上/下半部分的全局时钟线(BUFG)。

MRCCs可以访问多个时钟区域和全局时钟树。MRCCs的功能与SRCCs相同,还可以驱动多时钟区域缓冲器(BUFMR)来访问多达三个时钟区域。如果不用作时钟,时钟输入管脚可以用作常规I/O。当用作常规I/O时,支持时钟的输入引脚可以配置为任何单端或差分I/O标准。时钟输入管脚可以连接到同一时钟区域的CMT,和该时钟区域的上下的CMT,但具有一定的限制。

(1)单个时钟驱动单个CMT

当时钟输入驱动单个CMT时,时钟输入管脚和CMT(MMCM/PLL)必须在同一时钟区域。

(2)单个时钟驱动多个CMTs

一个时钟输入可以驱动同一列中的其他CMT。在这种情况下,一个MMCM/PLL必须被放置在与时钟输入管脚相同的时钟区域中。在相邻区域放置附加的CMT是更为优化的,但是在同一列中,可以驱动比一个CMT更远的CMT。CMT中使用的资源必须相同,才能自动放置此配置而不使用CLOCK_DEDICATED_ROUTE约束。如果需要混合MMCMs/PLL,则应首先将其置于同一CMT中。如果有必要从不在同一时钟区域的时钟输入管脚驱动CMT,并且在与时钟输入管脚相同的时钟区域中没有MMCM/PLL,则必须设置属性CLOCK_DEDICATED_ROUTE = BACKBONE。在这种情况下,MMCM或PLL不能正确地将输出与输入时钟对齐,即存在时钟偏移。在同一列中专用资源驱动CMT是有限制的。一些Xilinx IP使用这些资源,从而使它们不可用于其他设计用途,并导致设计无法布线。如果到其他时钟区域的专用路由不可用,则将CLOCK_DEDICATED_ROUTE设置为FALSE将允许使用本地互连逻辑,尽管这会导致更长的无补偿延迟。如果由普通的IO管脚驱动全局时钟资源,比如BUFG或者MMCM,则CLOCK_DEDICATED_ROUTE = FALSE。

(3)时钟输入管脚放置规则

在创建初始设计之前,手动选择支持时钟的输入引脚时,有两个主要考虑因素:

确保支持时钟输入可以连接到所需的时钟资源。表所示的布局规则确保连通性。

确保所需的时钟资源是可用的,并且没有被设计的另一部分使用。确保通过时钟输入管脚进入的外部时钟和来自IP的内部生成时钟不会在访问内部时钟网络时发生冲突,最好的方法是构建包含所需时钟网络和IP的初始设计,并通过实现工具运行它。这大大增加了检查和信心,即引脚不需要由于时钟原因而改变。

遵循下表放置规则,以确保具有时钟输入引脚选择能够访问所需的内部时钟网络。每个I/O Bank位于在一个时钟区域中。注:通过确保正确选择具有时钟输入引脚的位置,避免昂贵的电路板重新设计和差的时钟时序。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?