本文来自本人微信公众号“花蚂蚁”,欢迎各位大佬关注。

原文链接:Verilog语法之三:变量

变量即在程序运行过程中其值可以改变的量,在Verilog HDL中变量的数据类型有很多种,这里只对常用的几种进行介绍。

网络数据类型表示结构实体(例如门)之间的物理连接。网络类型的变量不能储存值,而且它必需受到驱动器(例如门或连续赋值语句,assign)的驱动。

如果没有驱动器连接到网络类型的变量上,则该变量就是高阻的,即其值为z。常用的网络数据类型包括wire型和tri型。这两种变量都是用于连接器件单元,它们具有相同的语法格式和功能。

之所以提供这两种名字来表达相同的概念是为了与模型中所使用的变量的实际情况相一致。

wire型变量通常是用来表示单个门驱动或连续赋值语句驱动的网络型数据,tri型变量则用来表示多驱动器驱动的网络型数据。

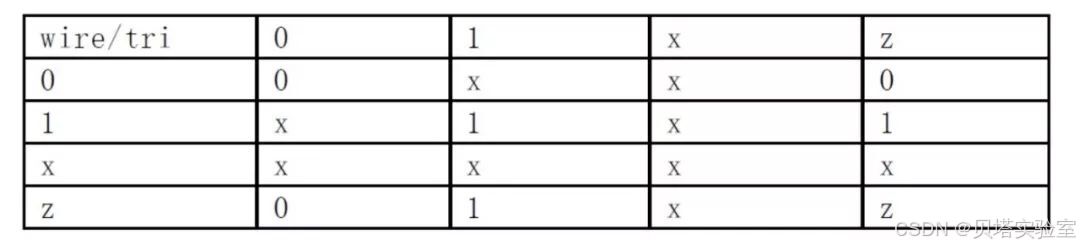

如果wire型或tri型变量没有定义逻辑强度(logic strength),在多驱动源的情况下,逻辑值会发生冲突从而产生不确定值。下表为wire型和tri型变量的真值表。

1.wire类型

wire型数据常用来表示用于以assign关键字指定的组合逻辑信号。Verilog程序模块中输入输出信号类型缺省时自动定义为wire型。wire型信号可以用作任何方程式的输入,也可以用作“assign”语句或实例元件的输出。

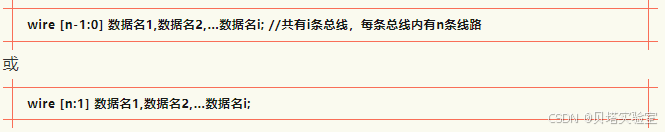

wire型信号的格式同reg型信号的很类似。其格式如下:

-

wire是wire型数据的确认符,[n-1:0]和[n:1]代表该数据的位宽,即该数据有几位。

-

最后跟着的是数据的名字。

-

如果一次定义多个数据,数据名之间用逗号隔开。声明语句的最后要用分号表示语句结束。

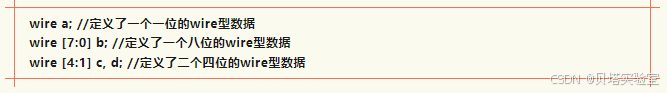

看下面的几个例子。

2.reg类型

寄存器是数据储存单元的抽象。寄存器数据类型的关键字是reg。通过赋值语句可以改变寄存器储存的值,其作用与改变触

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2530

2530

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?