文章目录

本篇文章介绍ATPG Tools pattern Types, ATPG pattern的类型,参考ug:

Basic Scan Patterns:

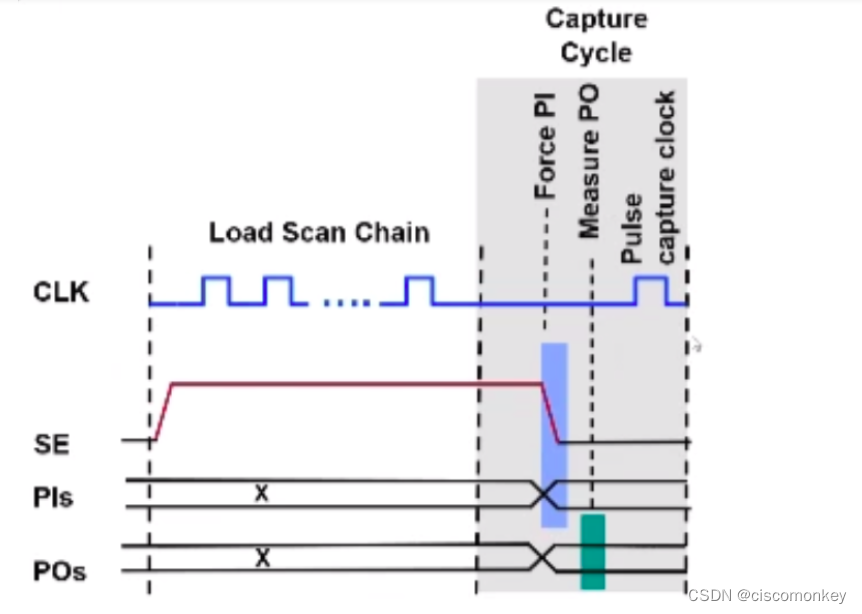

默认情况下工具是会先生成basic scan pattern,basic scan pattern是将一组values 给所有的scan cells( load in),以及 primary PI,另外再所有的primary output 以及scan cell上进行观察(measure po), 工具会使用默认的scan clock 来抓取数据到observable scan cells(capture_clock_on,capture_clock_off) . 每一只pattern都是独立的。

basic pattern遵循下面的events:

1、load values into scan chains.

2、 Force values 在所有的non-clock primary inputs(with clocks off and constrained pins at their constrained valued)

3、measure all primary outputs(except those connected to scan clocks)

4、pulse a capture clock or apply seleced clock procedure.

5、unload values from scan chains

load in -->force PI–>measure PO–>capture—>load out

Clock PO Patterns

Clock Sequential Patterns

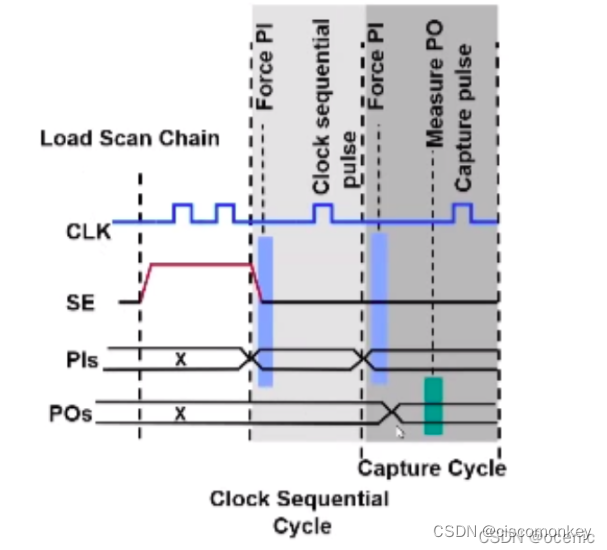

对于sequential pattern来说,这是非常常见的一种pattern,但初学者往往不是很理解这种pattern的行为。

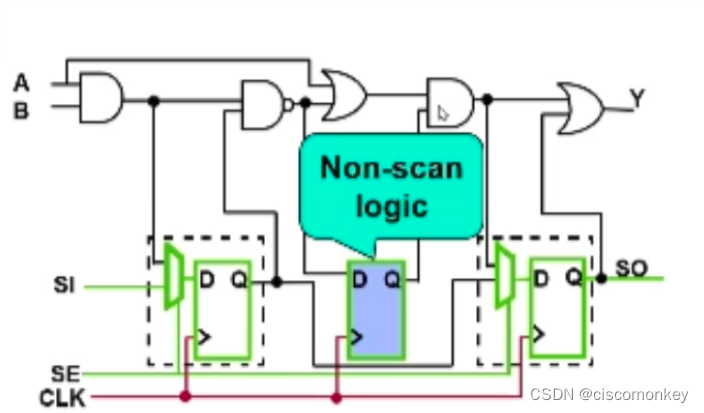

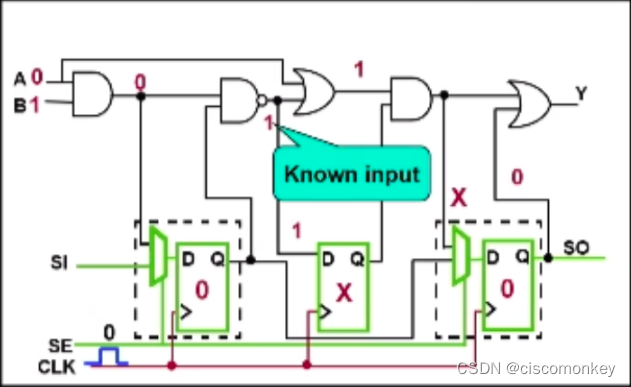

如下图所示,我们可以看到电路中有一个non-scan cell,而sequential pattern就是为了提高non-scan cell的coverage的。

上图中存在一个non-scan cell作为组合逻辑的连接部分,那我们知道对于上图中的non scan cell的Q端口是没法给出值的,因为load in 只会load SDFF,此时两个寄存器的Q都会有值存在了,然后我们即使进行force PI, measure PO,然后load out的时候是比较的是Scan out,所以在capture时钟,即使这个non-scan cell抓到了一个非X的值,再继续load out的时候也只会比较scan out上的值。

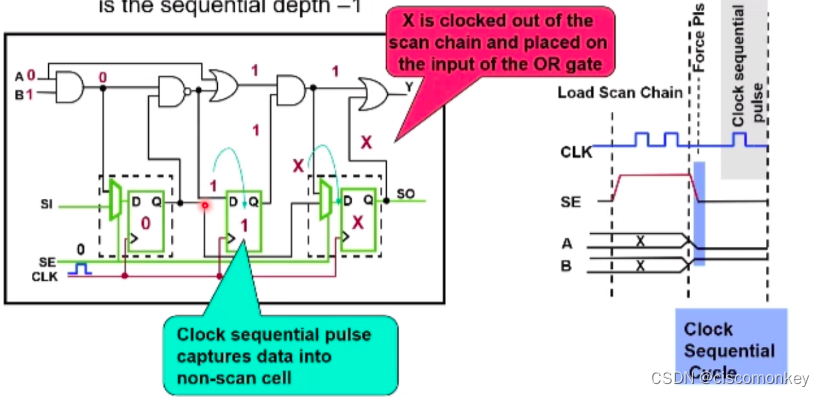

sequential pattern在测试时候的event包括了:

1、load scan chain

2、apply clock sequential cycle : 重复force PI–> pulse clock N次,此时N为时序深度-1

3、apply capture cycle : force PI measure ,PO pulse ,capture clock

4、unload

工具会自动的识别sequential depth element

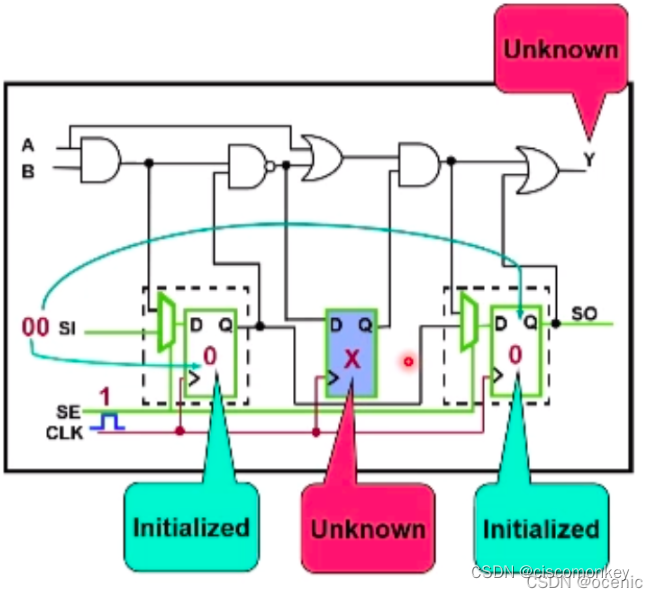

如上图中,我们shift in进去值00,然后进行force PI, 但是此时我们知道这个non-scan cell仍然是X态。即使我现在measure PO, 那么我此刻Y端口仍然是unknow。接下来,我要做capture动作,然后load out,此时我比值比的scan out chain上的值。也就是说整个过程因为我的non scan cell 为X,而影响了我的比值为X,从而影响了cov。

如上图所示,进入sequential cycle, 通过force PI, 此刻,non scan cell的D端口将会有值。

在sequential cycle中,打一个sequential cycle。此刻,non scan cell将会capture到值。而此刻X值传到了最后一级SDFF的D端

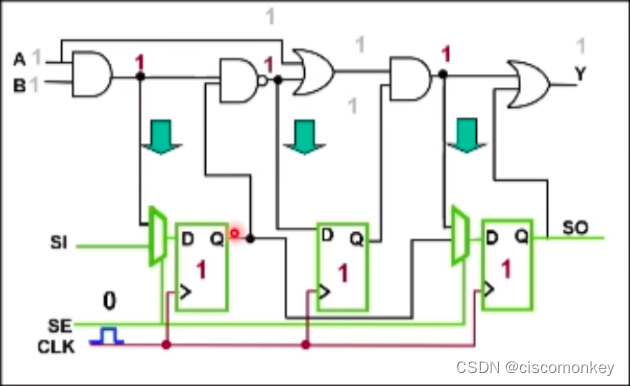

如上图所示,此刻non-scan cell的值已经不再是X了,已经具备了确认的值。此刻我们再进入apply capture clock,在capture cycle的时候进行force PI measure PO,给一个capture pulse将逻辑中的值capture到扫描链中。

至此,我们第一次force PI, 然后sequential pulse是为了将灌入non scan cell的值, 第二次PI才是真正用于capture的值。

如上图所示,是将capture到的值load out出来。

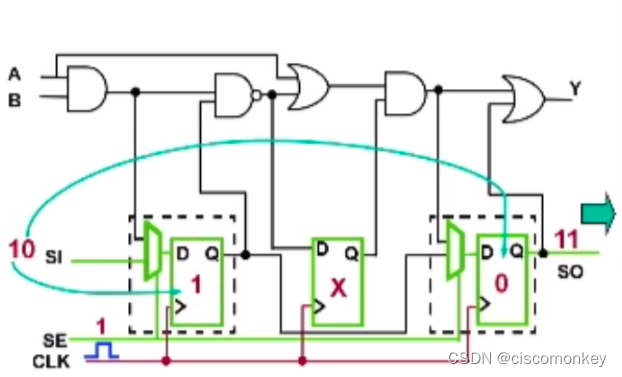

clock PO pattern

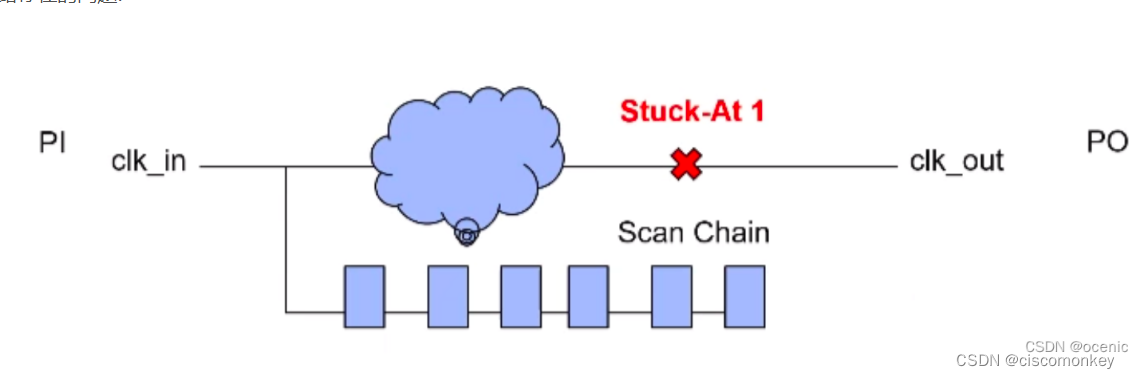

如下图所示,clock PO patetrn指的是,哪些时钟经过组合逻辑,然后直接连接到PO。这种情况是可以测到stuck at 1的,但是不能够测试到stuck 0,为什么这么说?

回想一下basic pattern的过程,force PI ,measure PO, 然后capture。值得注意的是force PI 和measure PO, 我们都知道发生在什么阶段,发生在没有时钟的阶段,SE拉低的阶段,换言之,就是说时钟能够为0. 在force PI和 measure PO的时候,因此我们可以测试下面的stuck at 1,因为时钟clk_in相当于可以被force PI为0.

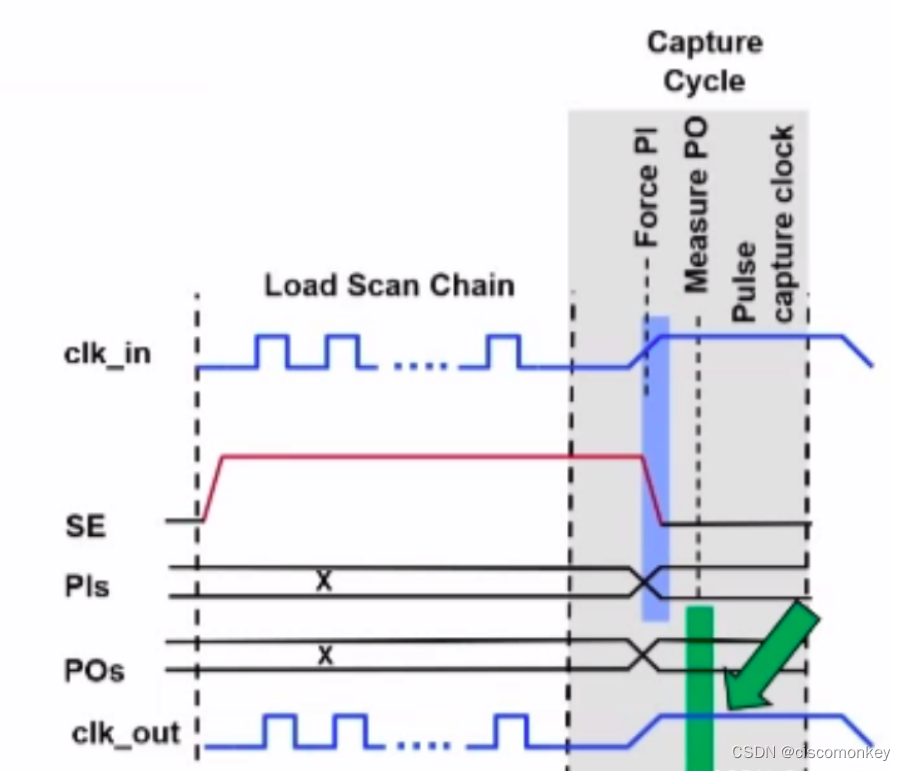

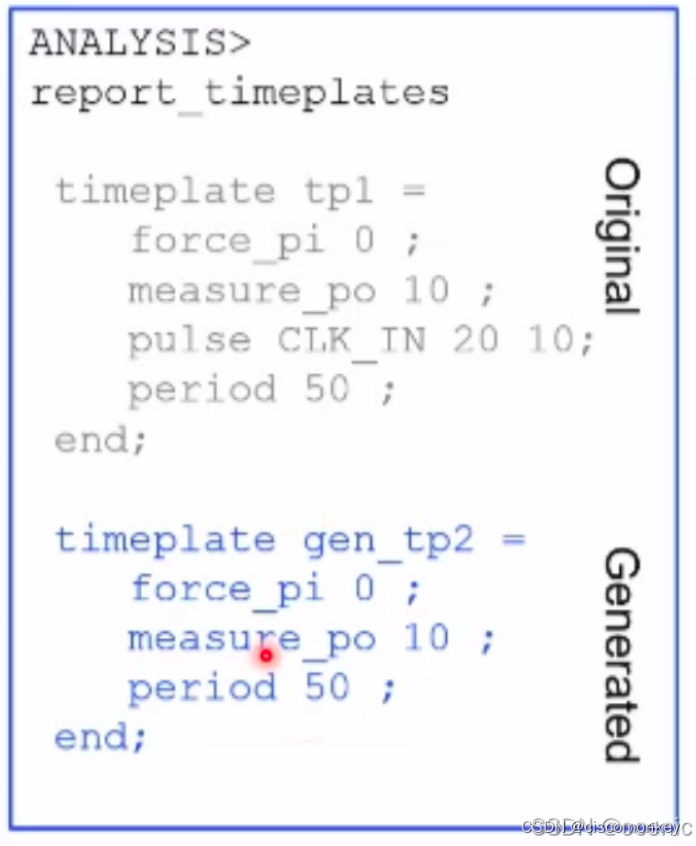

因此,为了解决这个问题,一个附加的timeplate被安排上了,这个timeplate会自动生成, 在basic pattern capture 或者load/unload的时候,它表现为一个规则的pulse,而在clock PO pattern这种pattern类型的capture cycle阶段,clk_in 表现为持续拉高的一个状态。

此时,我们在force PI 就可以force一个高电平的值,在measure PO就可以观察clk_out了。

report_timeplates

这篇文章讲解得非常好,我也结合对这篇文章的理解,再次赘述,如原CSDN博主有异议,请联系我。

参考优质文章

如果对于ATE机台来说也要看是否支持multiple timeplate,对于不支持的,只能cut off掉,但是对coverage覆盖率的影响很小。

set_pattern_type -clock_po off

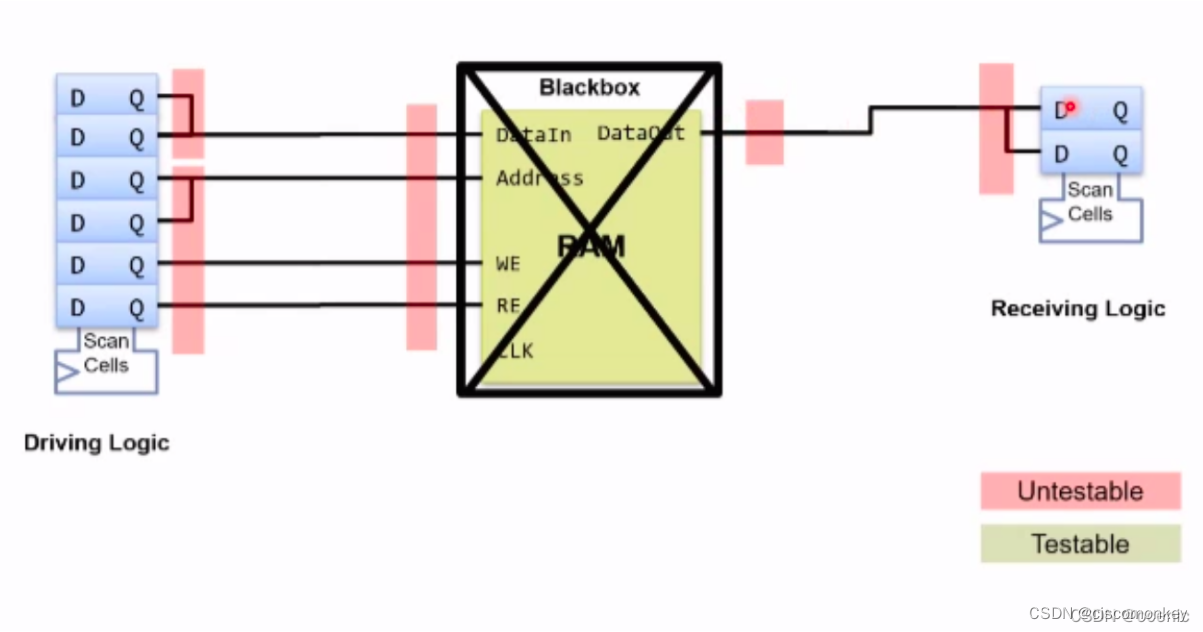

Testing Around RAMS(如何测试memory周边的logic)

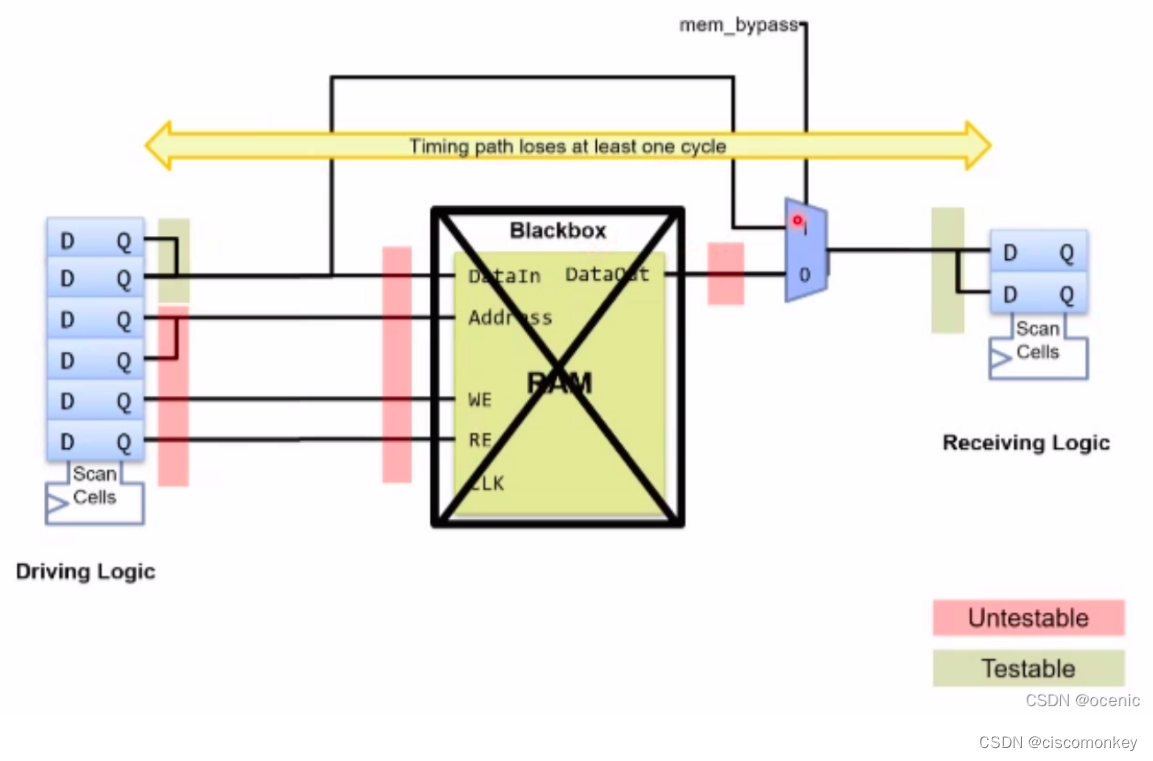

如下图所示,是通过bypass memory来实现memory周边的测试的。

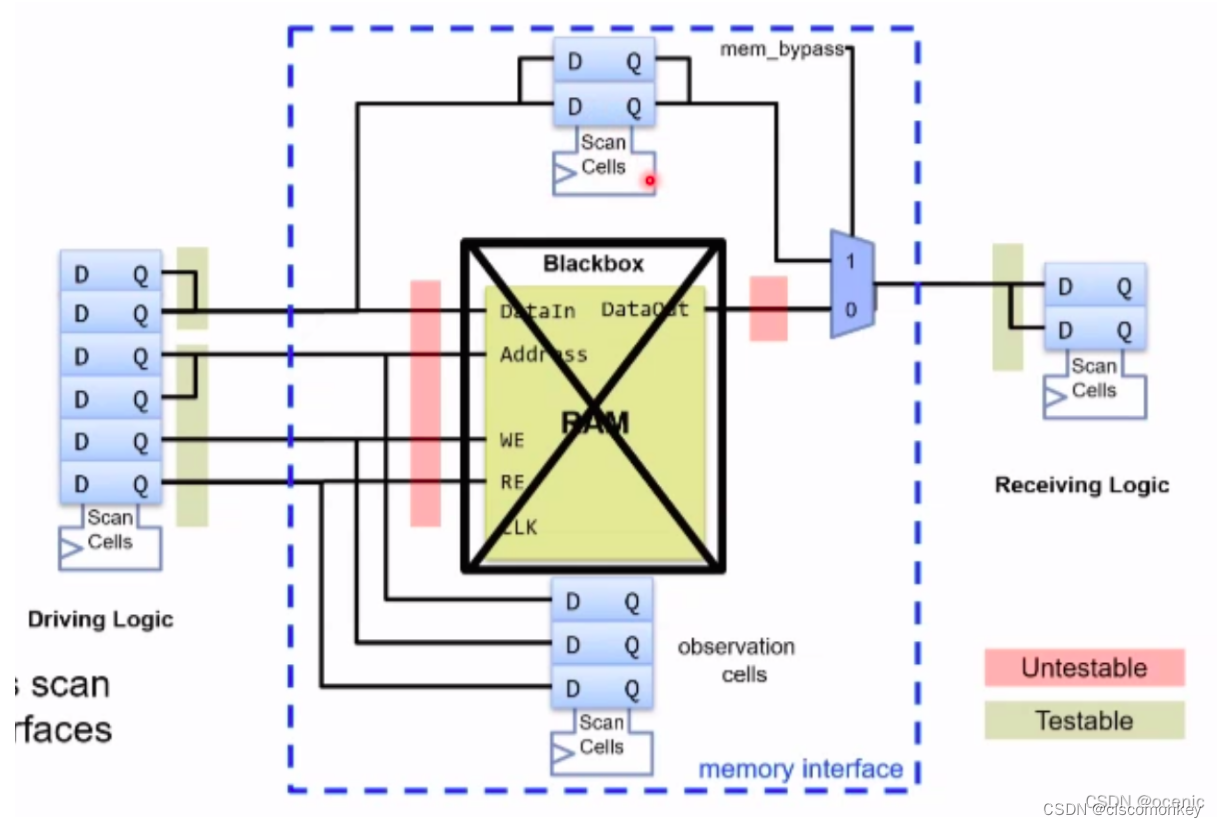

但是我们可以看到上面的timing path跨度非常大,因此,我们可以按照下图所示进行添加FlipFlop, 此外如下图所示,我们还可以看到下面的observe cells 是用来observe的,也是因为增加了mem_bypass的效果。

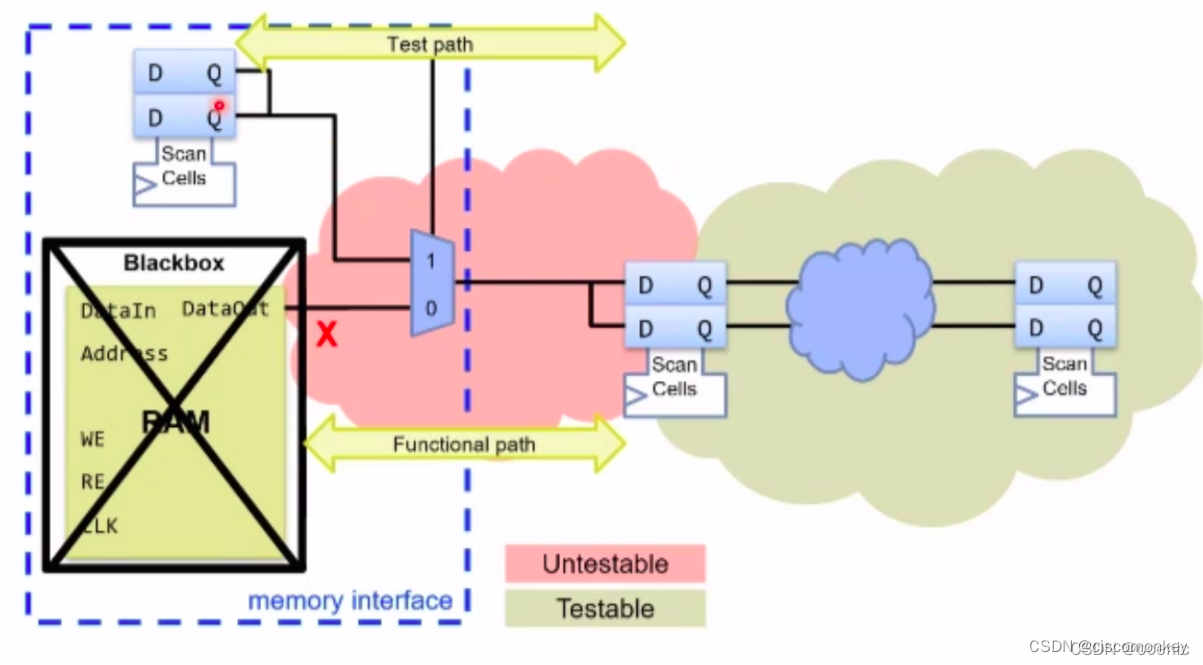

如上图所示,即使加了bypass电路只能保证后面蓝色的一堆变得可测,mux的部分仍然是不可测的。

278

278

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?